# THE CORA TENSOR COMPILER: COMPILATION FOR RAGGED TENSORS WITH MINIMAL PADDING

Pratik Fegade <sup>1</sup> Tianqi Chen <sup>12</sup> Phillip B. Gibbons <sup>1</sup> Todd C. Mowry <sup>1</sup>

#### ABSTRACT

There is often variation in the shape and size of input data used for deep learning. In many cases, such data can be represented using tensors with non-uniform shapes, or ragged tensors. Due to limited and non-portable support for efficient execution on ragged tensors, current deep learning frameworks generally use techniques such as padding and masking to make the data shapes uniform and then offload the computations to optimized kernels for dense tensor algebra. Such techniques can, however, lead to a lot of wasted computation and therefore, a loss in performance. This paper presents Cora, a tensor compiler that allows users to easily generate efficient code for ragged tensor operators targeting a wide range of CPUs and GPUs. Evaluating Cora on a variety of operators on ragged tensors as well as on an encoder layer of the transformer model, we find that Cora (i) performs competitively with hand-optimized implementations of the operators and the transformer encoder and (ii) achieves, over PyTorch, a  $1.6\times$  geomean speedup for the encoder on an Nvidia GPU and a  $1.86\times$  geomean speedup for the multi-head attention module used in transformers on an ARM CPU.

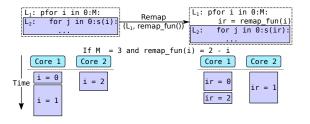

Figure 1. An example operation on ragged tensors.

## 1 Introduction

Deep learning (DL) is used for a variety of computational tasks on different kinds of data including sequential data like text (Tai et al., 2015; Vaswani et al., 2017), audio (van den Oord et al., 2016) and music (Briot et al., 2017; Huang et al., 2018) and spatial data like images (He et al., 2016). Simultaneously, DL models have become more and more computationally expensive. More efficient execution of these models is, therefore, a priority.

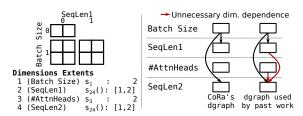

There is often variation in the sizes of the data that we process using DL. Images can be of different resolutions, textual sentences and documents can be of different lengths, and audio can be of different durations. Processing such data exhibiting variation in shape, or *shape dynamism* (Shen et al., 2020), using the same model and further, as part of the same mini-batch is therefore important. An example elementwise operation on such data is shown in Fig. 1, where the slices of the inner dimension of tensor A have variable sizes. Such tensors and operators are referred to as *ragged tensors* and *ragged operators* respectively. Note

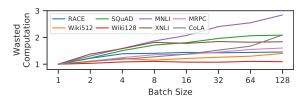

Figure 2. Wasted computation due to padding in a transformer encoder layer.

how the shape dynamism translates to a variable bound for loop L2 which iterates over the variable-sized tensor slices.

Past work has developed hand-optimized kernels to accelerate some important ragged applications such as batched matrix multiplication with variable dimensions (Li et al., 2019; Nath et al., 2010), triangular matrix multiplication (Charara et al., 2016) and the widely-used transformer (Vaswani et al., 2017) models (Eff; FT). Such hand-optimized kernels, however, require substantial development effort and, hence, are available only for a few operators. Further, they are not portable across different hardware substrates, which is problematic due to the rapid pace of innovation in DL hardware.

While some DL frameworks have started providing support for ragged operators recently (TFR; PTN), it is quite limited (TFI; PTI; NTL) as discussed in §8. Therefore, frameworks usually rely on efficient dense tensor algebra kernels implemented in vendor libraries such as cuDNN (Chetlur et al., 2014) and oneDNN (one) or generated by tensor compilers such as TVM (Chen et al., 2018a) to target parallel hardware. Padding (illustrated in the top right of Fig. 1) and

<sup>&</sup>lt;sup>1</sup>Carnegie Mellon University, Pittsburgh, USA <sup>2</sup>OctoML. Correspondence to: Pratik Fegade <ppf@cs.cmu.edu>.

*Table 1.* Comparison between CORA and current solutions for ragged operations. TC stands for tensor compilers.

| Framework            | Portability | Operator impl. effort | Padding | Performance |

|----------------------|-------------|-----------------------|---------|-------------|

| Dense TC             | High        | Low                   | Full    | Low         |

| Sparse TC            | High        | Low                   | Minimal | Low         |

| Dense vendor libs.   | Low         | High                  | Full    | Low         |

| Hand-optimized impl. | Low         | High                  | Minimal | High        |

| CORA                 | High        | Low                   | Minimal | High        |

masking<sup>1</sup> are therefore commonly used to eliminate shape dynamism in ragged tensors and enable the use of vendor libraries or dense tensor compilers (Hug, 2020).

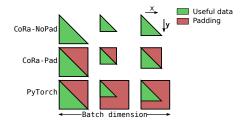

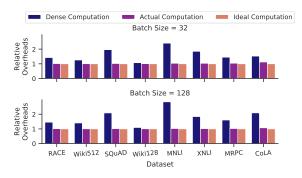

Padding and masking, however, lead to wasted computation as the padding or the masked data points are discarded after execution. Fig. 2 plots the relative amount of computation (computed analytically in FLOPs) involved in the forward pass of an encoder layer of the transformer model<sup>2</sup> with and without padding. We see that padding leads to a significant increase in the computational requirements of the layer, especially at larger batch sizes, increasing computation in an already computationally expensive model.

Thus, current solutions for efficient ragged operator execution are unsatisfactory. Hence, we propose a compiler-based solution enabling easy and more portable generation of performant code for ragged operators. While sparse (Tian et al., 2021; Kjolstad et al., 2017) and dense (Chen et al., 2018a; Vasilache et al., 2018; Ragan-Kelley et al., 2013; Baghdadi et al., 2019) tensor compilers have been well-studied, it is not straightforward to apply these techniques to ragged tensors, due to the following challenges:

- **C1 Irregularity in generated code:** While the data in ragged tensors are densely packed, the variable loop bounds can lead to irregular code, often causing a loss of performance on hardware substrates such as GPUs.

- C2 Insufficient compiler mechanisms: Representing transformations on loops with variable bounds and on tensor dimensions with variable-sized slices is not straightforward due to the dependencies that exist among loops and tensor dimensions respectively in ragged operators. Further, optimization decisions made by sparse tensor compilers may not always work for ragged tensors as sparse tensors are much sparser than ragged tensors.

- C3 Ill-fitting computation abstractions: There is a mismatch between the interfaces and abstractions provided by current compilers and ragged operators. Such operators cannot be expressed in dense compilers, while sparse compilers do not adequately provide ways to express information relevant to efficient code generation.

With these challenges in mind, we present CORA (Compiler for Ragged Tensors), a tensor compiler which allows one to express and optimize ragged operations to easily target a variety of substrates such as CPUs and GPUs. To overcome challenge C1, CORA enables minimal padding of ragged tensor dimensions (§4.1) in order to generate efficient code for targets such as GPUs as well as to specify thread remapping strategies to lower load imbalance (§4.1). CORA uses uninterpreted functions (Strout et al., 2018) to symbolically represent variable loop bounds and scheduling operations on the same (§5.1). CORA's mechanisms (such as its storage lowering scheme discussed in §5.2) and optimizations are specialized for ragged tensors thereby tackling C2. Further, CORA provides simple abstractions to convey information essential to efficient code generation such as padding or thread remapping specifications and raggedness patterns of tensors to the compiler (§4). This overcomes challenge C3.

CORA enables efficient code generation for ragged operators by significantly reducing padding (§7). As part of CORA's implementation, we reuse past work by extending a tensor compiler (Ragan-Kelley et al., 2013; Chen et al., 2018a; Baghdadi et al., 2019; Kjolstad et al., 2017) and thus, provide familiar interfaces to CORA's users. It also makes it easy in the future to use auto-scheduling (Mullapudi et al., 2016; Adams et al., 2019; Chen et al., 2018b; Zheng et al., 2020a; Singh et al., 2021) for optimizing ragged tensor operations. Table 1 compares CORA with alternatives that are or could be used for ragged operators. Only CORA achieves high performance and portability, with low operator implementation effort (and minimal padding).

In summary, this paper makes the following contributions:

- 1. We present CORA, a tensor compiler for ragged tensors. To our knowledge, CORA is the first tensor compiler that allows efficient computation on ragged tensors.

- 2. As part of the design, we generalize the API, abstractions and the mechanisms of tensor compilers and propose new scheduling primitives for ragged tensors.

- 3. We evaluate CORA on a variety of ragged operators. For a transformer encoder layer, we perform 1.6× better than PyTorch (Paszke et al., 2019) and as well as FasterTransformer (FT), a highly optimized transformer implementation, on an Nvidia V100 GPU. On an ARM CPU, we obtain overall speedups of 1.86× and 1.89× over PyTorch and TensorFlow (Abadi et al., 2016), respectively, on the multi-head attention (MHA) module (Vaswani et al., 2017) used in transformers.

## 2 CORA OVERVIEW

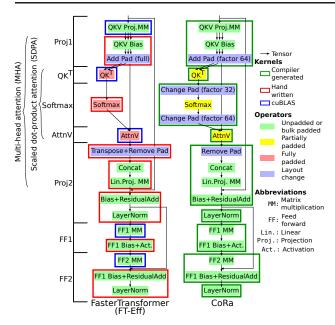

CORA's compiler-based approach enables the generation of performant code in a portable manner. This is reflected in Fig. 3, which compares CORA's implementation of a trans-

<sup>&</sup>lt;sup>1</sup>Masking involves setting some tensor elements to a special value so that these elements are ignored in computations.

<sup>&</sup>lt;sup>2</sup>The hyperparameters used are the same as those in §7.2.

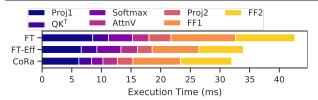

Figure 3. FasterTransformer (FT-Eff) and CoRA implementations of a transformer's encoder layer. Note how CoRA's fully compiler-based implementation uses only partial padding for SDPA as opposed to FasterTransformer's fully padded implementation. CoRA also enables more operator fusion (including fusing all the padding change operations) as opposed to FasterTransformer, which cannot do so in all cases as it relies on vendor libraries.

former encoder layer with FasterTransformer. The highlyoptimized FasterTransformer relies heavily on kernels implemented in cuBLAS (Nvidia's BLAS library), which are shown as blue outlines in the figure, and on manually implemented kernels, shown as red outlines. On the other hand, CORA's implementation exclusively employs compiler generated kernels (shown as green outlines), making it more portable. Further, CORA's compiler approach allows it to exploit more kernel fusion opportunities, evident from the fact that CoRA's implementation launches nine kernels as opposed to FasterTransformer's twelve. Both the implementations in the figure use minimal padding for all operators except for those in the scaled dot-product attention (SDPA) sub-module, where CORA's specialized approach enables it to get away with lower padding as compared to FasterTransformer. We further discuss these implementations in §7.

CORA's ability to generate performant code that employs minimal padding in a portable manner as we saw above relies on the following two insights:

- I1 In ragged operations, the pattern of raggedness is usually known before the tensor is actually computed, and is the same across multiple tensors involved in the operation.

- I2 Ragged tensors, like dense tensors, allow O(1) accesses (§5.2). This is unlike sparse formats such as compressed sparse row (CSR), where accesses require a search over an array. The HASH (Chou et al., 2018) sparse format,

while allowing O(1) accesses, is unsuitable for accelerators such as GPUs due to its highly irregular storage.

Insight I1 allows CORA to precompute the auxiliary data structures needed to access ragged tensors without knowledge of the computation (or values of its input tensors) that produces the ragged tensor. This and insight I2 enable CORA to generate efficient code for ragged operations.

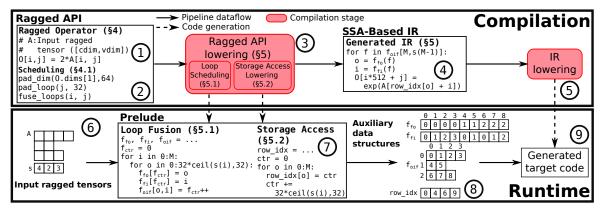

Let us now look at CORA's overall compilation and execution pipeline, as illustrated in Fig. 4. The user first expresses (1) and schedules (2) their computation using an API similar to that of past tensor compilers (§4). This specification of the computation and the scheduling primitives are then lowered (3) to an SSA-based IR (4). As part of this lowering step, CORA generates code (7) to initialize some auxiliary data structures it needs to be able to lower accesses to ragged tensors (§5.2) and to enable loop fusion in ragged loop nests (§5.1). We refer to this code as the *prelude* code. Compilation then continues with CORA lowering tensor accesses to raw memory offsets by making use of the data structures generated by the prelude. Finally, CORA generates (5) target-dependent code (9) such as C or CUDA C++. During execution, the formats of the input ragged tensors (6) are first processed by the generated prelude code (7) which creates the auxiliary data structures (8). This prelude code is not computationally expensive (§7.4) and hence is executed on the host CPU. These data structures and the ragged tensors are then passed to the generated target dependent code (9) which executes on devices such as CPUs or GPUs.

We will now look these stages in more detail below.

## 3 TERMINOLOGY

Ragged operators have one or more loops with bounds that are functions of iteration variables of outer loops. We refer to such loops as *variable loops* or *vloops* while loops with constant bounds are referred to as constant loops, or *cloops*. A loop nest with at least one vloop is referred to as a vloop nest. Further, tensors can be stored in memory with or without padding. When stored without full padding, the size of some tensor dimensions depends on outer tensor dimensions. Such dimensions are referred to as *variable dimensions*, or *vdims* and those with constant sizes are *constant dimensions* or *cdims*. A tensor stored such that it has no vdim (i.e. a fully padded tensor) is referred to as a dense tensor, while a tensor with at least one vdim is a ragged tensor. Note that ragged tensors may be padded to some extent.

#### 4 CORA'S RAGGED API

CORA provides a simple API similar to that of past tensor compilers, as seen in Listing 1, which expresses the example computation from Fig. 1 in CORA. Apart from

Figure 4. Overview of CoRA's compilation and runtime pipeline.

describing the computation as in a dense tensor compiler, CORA also requires the user to specify the raggedness dependences of the computation (highlighted in Listing 1). This involves specifying vloop bounds as functions of outer loop variables and vdim extents as functions of indices of outer tensor dimensions. Given this information, CORA automatically computes any derived data structures required (§5), making it easy for users to express their computations. CORA uses identifiers called *named dimensions* (discussed further in §B.3 of the appendix) to name loops and corresponding tensor dimensions and to specify relationships between them. For example, the loop extent defined on line 7 in the listing states the dependence on the outer loop, referred to by the named dimension batch\_dim.

```

1 ############## Operator Description ###############

BS = var('M')

# Batch size

# Declare named dimensions

batch_dim, len_dim = Dim(), Dim()

# Loop: Specify vloop extents

lens = input_tensor((BS,))

l_ext = Extent([batch_dim],

lambda b: lens[b])

loop_exts = [BS, l_ext]

# Storage: Specify vdim extents

10 s_ext = Extent([batch_dim], lambda b: lens[b])

11 storage_format = [BS, s_ext]

12 # Define input ragged tensor

13 dims = [batch_dim, len_dim]

14 A = input_tensor(dims, storage_format)

15 # Express computation

16 O = compute(dims, loop_exts, lambda i, j: 2*A[i, j])

17 ############ Scheduling primitives #########

18 pad_loop(0.loops[1], 32)

pad dimension(O.dimensions[1], 64)

fuse_loops(0.loops[0], 0.loops[1])

```

Listing 1. Operator in Fig. 1 expressed in a simplified version of CoRA's API.

## 4.1 Scheduling Primitives

In order to optimize the expressed computation, CORA provides all the scheduling primitives commonly found in tensor compilers. Below, we describe some salient features and points of departure from past tensor compilers.

Loop Scheduling: Both cloops and vloops can be sched-

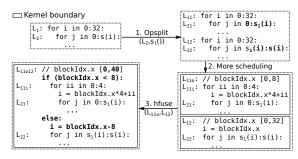

Figure 5. Operation splitting and horizontal fusion. The loop  $\mathbb{L}_2$  is first split in step 1 using operation splitting thus creating two loop nests. The two loop nests are then horizontally fused together (step 3) so they execute concurrently as part of single kernel.

uled in CORA. We saw how a vloop, say  $L_v$ , has a loop bound that is a function of the iteration variables of one or more outer loops, say  $L_1$  to  $L_k$ . CORA currently does not allow reordering such a loop  $L_v$  beyond any of the loops  $L_1$  to  $L_k$ . While possible with the introduction of conditional statements, we have not found a use case for such reordering.

**Operation Splitting:** It can sometimes be beneficial to differently schedule different iterations of a loop in a vloop nest in order to more optimally handle the variation in loop bounds. CORA allows one to split an operation into two or more operations by specifying split points for one or more of its loops, as Fig. 5 shows. In our evaluation (§7.3), we use this transformation in conjunction with horizontal fusion (described below) to better handle the last few iterations of a tiled loop without the need for additional padding in the QK<sup>T</sup> and AttnV operators in the transformer layer (Fig. 3).

**Horizontal Fusion:** Past work (Li et al., 2020) has proposed horizontal fusion, or *hfusion* for short, as an optimization to better utilize massively parallel hardware devices such as GPUs by executing multiple operators concurrently as part of a single kernel. With CORA, we implement this optimization in a tensor compiler for the outermost loop of two or more operators. HFusion enables the concurrent

execution of the multiple operators that result from using the operation splitting transform described above.

Loop and Storage Padding: Despite the overheads of padding, a small amount of it is often useful in order to generate efficient vectorized and tiled code by eliding conditional checks. Accordingly, CORA allows the user to specify padding for vloops and vdims as multiples of a constant. For example, on line 18 of Listing 1, the vloop associated with the dimension len\_dim is asked to be padded to a multiple of 32 while the corresponding dimension of the output tensor is specified to be padded to a multiple of 64 on line 19. Such independent padding specification for loops and the underlying storage is allowed as long as the storage padding is at least as much as the loop padding (this ensures that the padded loop nest never accesses non-existent storage). This ability allows CORA to fuse padding change operators as is illustrated in Fig. 3. We show in §7.4 that this partial padding does not lead to much wasted computation.

**Tensor Dimension Scheduling:** CORA allows users to split, fuse and reorder dimensions of dense and ragged tensors. This can enable more optimal memory accesses. Fusing tensor dimensions in a way that mirrors the surrounding loop nest can allow for simpler memory accesses (§5.1).

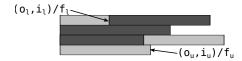

Load Balancing: The variable loop bounds in a vloop nest can lead to unbalanced load across execution units. As proposed by past work (Gale et al., 2020) on sparse tensor algebra, CoRA allows the user to redistribute work across different parallel processing elements by specifying a *thread remapping policy*. Given a parallel loop, this allows the user to specify a mapping between the loop iterations and the thread id (illustrated in Fig. 14 in the appendix). Depending on the hardware thread scheduling policy, this can influence the order in which iterations of the loop are scheduled and lead to non-trivial performance gains as shown in §7.1.

In conclusion, CORA provides familiar and simple interfaces to users, extended with a few scheduling primitives and abstractions specific to ragged tensors, enabling their application to support (efficient) ragged operations.

### 5 CORA'S RAGGED API LOWERING

We now discuss some aspects of CORA's Ragged API lowering that generates the SSA-based IR as shown in Fig 4.

#### 5.1 Loop and Tensor Dimension Fusion

Consider the ragged loop nest shown on the top left corner of Fig 6. The loop bound of the inner loop Li is a function s() of  $\circ$ , the iteration variable of the outer loop Lo. The loop Lf obtained by fusing Lo and Li is shown on the right of the figure. The loop bound F of the fused loop would be equal to  $\sum_{o=0}^{M} s(o)$ . Further note that while we

```

fuse(Lo,Li)

for o in 0:M:

for i in 0:s(o):

// Prelude Code

f_{fo}, f_{fi}, f_{oif} = \dots

f_{ctr} = 0

T[o,i] = ...

// Prelude Code

f_{fo}, f_{fi}, f_{oif} = \dots

f_{ctr} = 0

o in 0:M:

for i in 0:s(o):

f_{f_0}[f_{ctr}] = 0

f_{f_i}[f_{ctr}] = i

f_{oif}[o,i] = f_{ctr}++

for o in 0:M:

for i in 0:s(o):

f_{fo}[f_{ctr}] = 0

f_{fi}[f_{ctr}] = i

// Computation

f_{oif}[o,i] = f_{ctr}++

= f_{oif}[M,s(M-1)]

for f

in 0:F

// Computation

F = f<sub>oif</sub>[M,s(M-1)]

Lf: for f in 0:F:

o,i = f_{fo}[f],f_{fi}[f]

T[o,i] =

T[f] = \dots

fuse dims(T,0,1)

```

Figure 6. Fusing vloops and tensor dimensions

have fused the loops Lo and Li, the tensor access T [o,i] in the body of the loop nest still uses variables o and i. Therefore, we need to compute the values of these two variables corresponding to the current value of f, the iteration variable of Lf. Because of the ragged nature of the loop nest, computing the loop bound F as well as the mapping between the iteration variables of the original and the fused loop nests is not straightforward. In CORA, we generate code to compute these quantities and variable relationships (shown in the right pane of Fig. 6) as part of the prelude which executes before the main kernel computation. We use vloop fusion as described above to implement the linear transformation operators (Proj1, Proj, FF1 and FF2) in the transformer encoder (Fig. 3) with minimal padding.

Suppose now that the tensor T in Fig. 6 has a storage format that mirrors the loop nest consisting of Lo and Li. This means that the 2-dimensional tensor has an outer cdim and an inner vdim the size of the  $i^{th}$  slice of which is s(i). Fusing these dimensions then enables CORA to simplify the tensor access as shown in the bottom left pane of the figure.

## 5.2 Storage Access Lowering

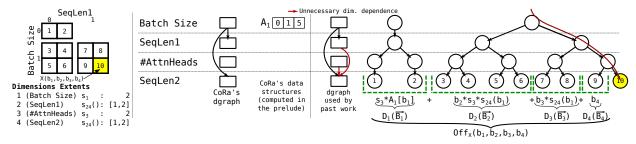

In this section, we briefly describe how CORA lowers accesses to ragged tensors. Consider the 4-dimensional attention matrix X involved in a batched implementation of MHA shown in the left pane of Fig. 7. Here, the first and the third dimensions are cdims and correspond to the batch size and the number of attention heads, respectively. The other two dimensions, corresponding to sequence lengths, are vdims. For X, the size of a slice for both these vdims is the same function  $(s_{24}())$  of the outermost batch dimension.

Due to the irregular nature of ragged tensor storage, we need some auxiliary data structures to be able to lower memory accesses to X. The scheme used by past work on sparse tensors (Smith & Karypis, 2015; Chou et al., 2018) for this purpose assumes that the number of non-zeros in a slice of a sparse dimension is, in general, a function of all of the outer dimensions. However, recall that for our example tensor X, the size of a slice of either vdim depends only on the

<sup>&</sup>lt;sup>3</sup>We use the same layout in CORA's implementation in §7.2.

Figure 7. CORA precisely models dimension dependences as compared to past schemes for sparse tensors.

outermost batch dimension. Being agnostic to such precise dependencies between tensor dimensions (as illustrated via the *dimension graphs*, or *dgraphs* in Fig. 7), past work would compute and store more auxiliary data as compared to Cora. Cora is lowering scheme also exploits the fact the data in a vdim slice is densely packed, which allows O(1) tensor accesses by cleverly precomputing certain memory offsets (the auxiliary data structures). We describe these lowering schemes further in the appendix in §B.1. In short, however, our storage access lowering scheme reduces the amount of auxiliary data that needs to be computed thus reducing the memory and computation overheads of the prelude code (§7.4), while allowing cheap tensor accesses.

## **6** IMPLEMENTATION

We prototype CoRA by extending TVM (Chen et al., 2018a) v0.6, a DL framework and a tensor compiler. Some details regarding this implementation are discussed below.

**Ragged API:** Our prototype allows vdims to depend on at most one outer tensor dimension. This is not a fundamental limitation and can easily be overcome, though we have not needed to for our evaluation. We implement the operator splitting and hfusion transforms for non-reduction loops.

Lowering: Our current prototype does not auto-schedule the expressed computation. The evaluation therefore uses implementations optimized using a combination of manual scheduling and grid search. For some operators, we auto-scheduled the corresponding dense tensor operator using past work (Zheng et al., 2020a) and manually applied the schedule to the ragged case. We find that this works well in most cases and therefore believe that the prototype could readily be extended with prior work on auto-scheduling. Our implementation currently expects users to correctly allocate memory (taking into account padding requirements as specified in the schedule) for tensors. Checks to report these problems can also, however, be easily implemented.

#### 7 EVALUATION

We now evaluate CORA against state-of-the-art baselines, first, on two ragged variants of the gemm (general matrix multiplication) operation in §7.1 and then on an encoder layer of the transformer model (Fig. 3) in §7.2. Our ex-

Table 2. Experimental environment (GCP: Google Cloud Platform)

| Hardware                                                                    | Software (All instances ran Ubuntu 20.04.)                                                                            |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Nvidia Tesla V100 GPU (GCP n1-standard-8 instance)                          | CUDA 11.1, cuDNN 8.2.1, PyTorch 1.9.0,<br>FasterTransformer v4.0 (commit dd4c071)                                     |

| 8 core, 16 thread Intel<br>CascadeLake CPU (GCP<br>n2-standard-16 instance) | Intel MKL (v2021.3)                                                                                                   |

| 8 core ARM Graviton2 CPU<br>(AWS c6g.2xlarge instance)                      | PyTorch 1.9.0a0+gitd69c22d and TensorFlow 2.6.0 (both with oneDNN 2.3 and Arm compute library 21.05), OpenBLAS 0.3.10 |

Table 3. Datasets used in our evaluation

| Dataset (Short name, if any)                | Min. / Mean / Max. SeqLength |

|---------------------------------------------|------------------------------|

| RACE (Lai et al., 2017)                     | 80 / 364 / 512               |

| English Wikipedia with SeqLen 512 (Wiki512) | 12/371/512                   |

| SQuAD v2.0 (Rajpurkar et al., 2018) (SQuAD) | 39 / 192 / 384               |

| English Wikipedia with SeqLen 128 (Wiki128) | 14 / 117 / 128               |

| MNLI (Williams et al., 2018)                | 9 / 43 / 128                 |

| XNLI (Conneau et al., 2018)                 | 9 / 70 / 128                 |

| MRPC (Dolan & Brockett, 2005)               | 21 / 59 / 102                |

| CoLA (Warstadt et al., 2019)                | 6 / 13 / 37                  |

perimental environment is described in Table 2. Below, we refer to the three platforms listed in the table as Nvidia GPU, Intel CPU and ARM CPU. Our evaluation is performed with single-precision floating point numbers.

## 7.1 Matrix Multiplication

We start by evaluating CORA's performance on the variablesized batched gemm (or vgemm) and the triangular matrix multiplication (or trmm) operators. As with all the implementations we compare against, the CORA implementations of these operators use fully padded storage for all tensors.

Variable-Sized Batched Gemm: The vgemm operator consists of a batch of gemm operations, each with different dimensions. For this operator, we evaluate CORA on the Nvidia GPU and Intel CPU backends and compare against hand-optimized implementations of vgemm and fully padded batched gemm in both cases. On the CPU, we compare against Intel MKL's implementations while on the GPU, we compare against past work (Li et al., 2019) on vgemm and cuBLAS's implementation of fully padded batched gemm. We use synthetically generated data where matrix dimensions are uniformly randomly chosen multiples of 128 in [512, 1408]. CORA's CPU implementation offloads the computation of inner gemm tiles to MKL, allowing us to obtain computational savings due to raggedness while also exploiting MKL's highly optimized microkernels.

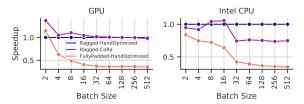

As Fig. 8 shows, CORA is effectively able to exploit raggedness on both CPUs and GPUs, performing as well as or better than the hand-optimized implementation on the GPU and obtaining better than 73% of the performance of MKL's vgemm for all batch sizes and performing better on a couple on the CPU. In all cases, CORA is significantly better than the fully padded gemm operations, which perform worse at higher batch sizes as there is more wasted computation as batch size goes up for the batch sizes evaluated.

Figure 8. CORA's vgemm performance compared against handoptimized implementations of vgemm and fully padded gemm, normalized to the Ragged-HandOptimized baseline.

Figure 9. CORA's trmm performance compared against cuBLAS's hand-optimized trmm and fully-padded gemm implementations.

Triangular Matrix Multiplication: A triangular matrix, i.e. a matrix where all the elements above (or below) the diagonal are zero, can be thought of as a ragged tensor because all non-zero elements in a row are densely packed and their number per row is a function of the row index. Operations on triangular matrices can, thus, be effectively expressed and optimized using CORA. In this section, we evaluate CoRA on the trmm operator wherein we multiply a square lower triangular matrix with a square dense matrix, on the Nvidia GPU. We compare against cuBLAS's trmm and fully padded gemm implementations. In trmm, the reduction loop is a vloop. In order to efficiently handle the last few iterations of this loop after tiling, we use operation splitting<sup>4</sup> (§4). Further, the raggedness in this loop leads to imbalanced load across the GPU thread blocks. We use thread remapping (§4.1) to schedule thread blocks with the most amount of work first, leading to more balanced load.

Fig. 9 shows the performance of the aforementioned cuBLAS implementations and three implementations CORA—CORA-unsplit-unbalanced, CORA-splitunbalanced and CORA-split-balanced-which progressively employ operation splitting and thread remapping, starting with neither. We see the trmm implementationsboth cuBLAS's and CoRA's—are beneficial as compared to cuBLAS's dense sgemm operator only for larger matrices. In all cases, however, the CoRA-split-balanced implementation performs within 81.3% of cuBLAS's hand-optimized trmm implementation. Operation splitting leads to a significant increase in performance by allowing CORA to elide conditional checks in the main body of the computation. Further, a better load distribution with thread remapping also helps CORA achieve performance close to cuBLAS.

Table 4. Transformer encoder layer execution latencies in ms for CORA, PyTorch and the two manually-optimized variants of Faster-Transformer on the Nvidia GPU. CORA's execution latencies include prelude overheads assuming a 6 layer transformer encoder.

| Dataset | Batch Size | PyTorch | FT    | CoRA  | FT-Eff |

|---------|------------|---------|-------|-------|--------|

|         | 32         | 12.22   | 11.0  | 8.22  | 8.61   |

| RACE    | 64         | 24.46   | 21.88 | 15.91 | 16.75  |

|         | 128        | 48.73   | 42.26 | 31.45 | 33.61  |

|         | 32         | 12.26   | 11.0  | 9.1   | 9.32   |

| Wiki512 | 64         | 24.52   | 22.12 | 17.4  | 17.85  |

|         | 128        | 48.72   | 42.43 | 32.17 | 33.66  |

|         | 32         | 8.17    | 7.56  | 4.15  | 4.69   |

| SQuAD   | 64         | 16.9    | 15.63 | 7.78  | 9.2    |

|         | 128        | 34.18   | 30.62 | 15.36 | 17.91  |

|         | 32         | 2.79    | 2.45  | 2.59  | 2.28   |

| Wiki128 | 64         | 5.12    | 4.61  | 4.72  | 4.35   |

|         | 128        | 10.1    | 9.29  | 8.86  | 8.54   |

|         | 32         | 2.22    | 2.04  | 1.11  | 1.03   |

| MNLI    | 64         | 4.44    | 4.06  | 1.89  | 1.93   |

|         | 128        | 9.53    | 8.86  | 3.53  | 3.78   |

|         | 32         | 2.76    | 2.45  | 1.56  | 1.5    |

| XNLI    | 64         | 5.13    | 4.62  | 2.94  | 2.86   |

|         | 128        | 10.03   | 9.3   | 5.62  | 5.49   |

|         | 32         | 1.85    | 1.73  | 1.32  | 1.27   |

| MRPC    | 64         | 3.76    | 3.48  | 2.6   | 2.36   |

|         | 128        | 7.42    | 6.89  | 4.55  | 4.55   |

|         | 32         | 0.67    | 0.57  | 0.59  | 0.44   |

| CoLA    | 64         | 1.02    | 0.93  | 0.77  | 0.63   |

|         | 128        | 2.37    | 2.18  | 1.26  | 1.17   |

## 7.2 The Transformer Model

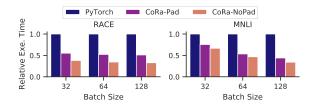

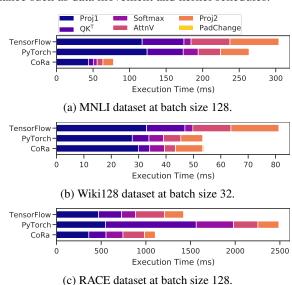

We now move on to look at how CORA performs on various modules of the transformer model. We mainly focus on the GPU backend as it is more commonly used for these models. We use a 6 layer model with a hidden dimension of 512 and 8 attention heads each of size 64. The encoder layer contains two feed-forward layers, the inner one of which has a dimension of 2048. These are the same hyperparameters used in the base model evaluated in (Vaswani et al., 2017). We use sequence lengths from some commonly used NLP datasets listed in Table 3.<sup>5</sup> We focus on larger batch sizes (32, 64 and 128) because, as we saw in Fig. 2, there is lesser opportunity to exploit raggedness for smaller batch sizes and hence other factors such as the quality of the schedules used in Corac implementations play a big role. In this section, Corac implementations use ragged tensor storage.

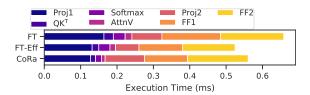

**Transformer Encoder Layer:** We first evaluate the forward pass latency of an encoder layer of the transformer model (Fig. 3). We compare CoRA's performance with that of FasterTransformer and an implementation in PyTorch, a popular DL framework, with TorchScript (Tor) enabled. All the operators in the encoder layer except the ones in the SDPA sub-module processthe hidden vectors associated with each word independently. Therefore, with manual effort, they can be implemented without any padding. The linear transformation operators Proj1, Proj2, FF1 and FF2 reduce to gemm operations in this case. FasterTransformer provides an option to perform this optimization, first introduced in EffectiveTransformers (Eff). We compare against

<sup>&</sup>lt;sup>4</sup>HFusion is not applicable here as the split loop is a reduction loop and executing the split operators concurrently would require atomic instructions, which our prototype does not yet support.

<sup>&</sup>lt;sup>5</sup>More details can be found in §D.1.

FasterTransformer both with and without this optimization. We refer to these two implementations as FT-Eff and FT, respectively. In the CORA implementation, this optimization is applied simply by loop fusion, analogous to the illustration in Fig. 6. In CORA's implementation however, we pad this fused loop so that its bound is a multiple of 64. In other words, we add a padding sequence to the batch to ensure that the sum of the sequence lengths is a multiple of 64. We refer to this kind of padding as *bulk padding* (Fig. 3). The relative amount of bulk padding added is usually quite low as the sum of sequence lengths in a batch is much higher.

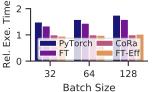

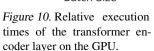

Table 4 shows the forward execution latencies for the encoder layer for the aforementioned frameworks and datasets. The auxiliary data structures computed by CoRA's prelude are shared across multiple layers of the model as the raggedness pattern stays the same across layers, depending only on the sequence lengths in the mini-batch. The execution times shown for CoRA include per-layer prelude overheads assuming a 6 layer model. We further look at these overheads in §7.4. As we can see, the CoRA implementation is competitive with the manually-optimized FT-Eff implementation for all datasets, even performing better in a few cases, and performs significantly better as compared to the fully-padded PyTorch and FT implementations. Fig. 10, which plots the overall performance of all these implementations for the batch sizes evaluated, makes this clear.

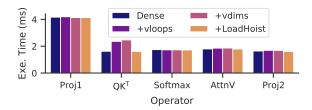

We now take a closer look at the FasterTransformer and CORA implementations which are sketched in Fig. 3.6 The FT implementation is similar to the FT-Eff implementation except it uses full padding for all operations. The CORA and FasterTransformer implementations differ in their operator fusion strategies. Therefore, the figure breaks the implementations down to the smallest sub-graphs that correspond to each other. Fig. 12 shows a breakdown of the execution times for these implementations for the RACE dataset and batch size 128 at the level of these sub-graphs. As Fig. 3 shows, the FT-Eff and CORA implementations differ significantly with respect to padding only in the SDPA sub-module where the FT-Eff implementation employs full padding while the CORA employs partial padding. We see, in Fig 12, that the CORA implementation performs better than FasterTransformer for all the SDPA operators (QK<sup>T</sup>, Softmax and AttnV) despite the fact that the latter is heavily hand optimized.<sup>8</sup> This is because CORA's ability to handle raggedness enables it to perform less wasted computation.

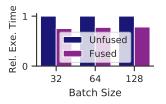

Figure 11. Relative MHA execution times with fused and unfused layout change operators.

For the remaining operators where both the CoRA and FT-Eff implementations employ little to no padding, we see that the CORA implementation is usually slower, but often close in performance to the FT-Eff implementation and significantly faster than the fully padded FT implementation. This is expected as FT-Eff calls into cuBLAS's extensively optimized gemm kernels for the linear transformation operators and into hand-optimized kernels for the rest. CORA's performance drops slightly for datasets with smaller sequence lengths as well as for smaller batch sizes. As we discuss in §D.8, this performance difference can be reduced by further optimizing the schedules used for the projection and feed forward operators in CORA's implementation for smaller batch sizes and sequence lengths. Further, we also note that the overheads associated with the prelude code and partial padding (§7.4) play a larger role in these cases, further contributing to increased execution latencies.

FasterTransformer's reliance on vendor libraries prevents it from fusing any of the gemm operations with surrounding elementwise operators, which CORA can due to its compiler-based approach. Specifically CORA can completely fuse all operators which add or remove padding in its implementation (as shown in Fig. 3). This is as opposed to the FT-Eff implementation, which can not. Fusing these padding change operators leads to a significant drop in CORA execution latency as seen in Fig. 11, which shows the execution latencies of the MHA module for the RACE dataset in CORA with and without this fusion enabled.

Masked Scaled Dot-Product Attention: The decoder layer of a transformer uses a variant of MHA called masked MHA wherein the upper half of the attention matrix is masked for all attention heads during training. This masking only affects the SDPA module, the operators in which can now be seen as computing on a batch of lower triangular matrices. We saw in §7.1 that CORA can effectively generate code for operations on triangular matrices. For batch size 128, an implementation of masked SDPA in CORA which exploits this masking performs 1.56× faster than an implementation which does not for the RACE dataset and  $1.29\times$ for the MNLI dataset. The benefits are less pronounced for the MNLI dataset, which has smaller sequence lengths, as we pad vloops to be multiples of a constant regardless of the dataset. We provide more data and discussion on the implementation of masked SDPA in §D.3 in the appendix.

<sup>&</sup>lt;sup>6</sup>FasterTransformer uses specialized implementations for different GPUs. In this paper, we limit our discussion to its implementation for the Nvidia V100 GPU we use for evaluation.

<sup>&</sup>lt;sup>7</sup>The raw data for this plot is listed in Table 9 in the appendix. <sup>8</sup>The execution times of the three SDPA operators is quadratically proportional to the sequence length, unlike the remaining operators which are linearly proportional. We discuss the performance of SDPA further in §D.8 of the appendix.

Figure 12. Breakdown of the encoder layer execution times for the RACE dataset at batch size 128. This data is obtained with profiling turned on and might deviate from Table 4.

*Table 5.* MHA execution latencies (in ms) on the ARM CPU. TF and PT refer to TensorFlow and PyTorch respectively.

| Dataset | ataset Batch Size 32 |     | Batch Size 64 |      |     | Batch Size 128 |      |      |      |

|---------|----------------------|-----|---------------|------|-----|----------------|------|------|------|

|         | PT                   | TF  | CORA          | PT   | TF  | CoRA           | PT   | TF   | CoRA |

| RACE    | 600                  | 355 | 288           | 1188 | 707 | 563            | 2388 | 1398 | 1111 |

| Wiki512 | 598                  | 358 | 325           | 1193 | 711 | 629            | 2386 | 1400 | 1157 |

| SQuAD   | 298                  | 227 | 119           | 722  | 458 | 235            | 1485 | 915  | 478  |

| Wiki128 | 52                   | 81  | 56            | 133  | 157 | 108            | 337  | 307  | 216  |

| MNLI    | 42                   | 66  | 21            | 100  | 133 | 41             | 280  | 302  | 80   |

| XNLI    | 52                   | 81  | 34            | 129  | 154 | 68             | 336  | 306  | 132  |

| MRPC    | 35                   | 60  | 28            | 81   | 122 | 55             | 176  | 241  | 108  |

| CoLA    | 11                   | 23  | 9             | 19   | 26  | 15             | 47   | 73   | 28   |

Memory Consumption: We find that the use of ragged tensors leads to an overall 1.78× drop in the size of the forward activations (computed analytically) of the encoder layer across all datasets at batch size 64 (more details in §D.5). The reduction, however, is not uniform across the datasets and those with higher sequence lengths, such as Wiki512 and Wiki128, see only small benefits. Forward activations often consume significant memory during training and ragged tensors can help alleviate memory bottlenecks along with other memory management techniques for training (Kirisame et al., 2021; Jain et al., 2020).

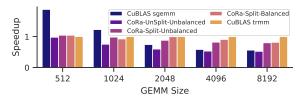

MHA Evaluation on ARM CPU: Table 5 shows the execution latencies for the MHA module in PyTorch, TensorFlow and CORA on the ARM CPU backend. Across the datasets and batch sizes evaluated, we see that CORA's implementation is overall 1.86× faster than PyTorch and 1.89× faster than TensorFlow. In this case, too, CORA's ability to save on wasted computation due to padding leads to significant performance gains over popular DL frameworks. We provide more details and discussion in §D.8 of the appendix.

## 7.3 Operation Splitting and Horizontal Fusion

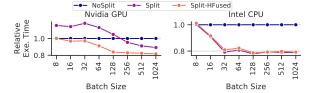

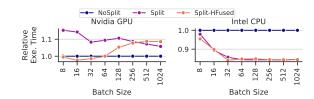

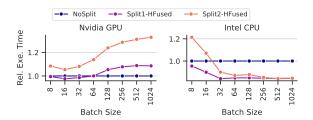

We now evaluate operator splitting and hfusion on the AttnV operator, which is an instance of the vgemm problem. AttnV has two vloops, one of which is a reduction loop. We apply the optimizations to the non-reduction vloop allowing

Figure 13. Benefits of operator splitting and horizontal fusion.

us to use a larger tile size (we use 64) without padding the vloop bound to be a multiple of this tile size. This especially benefits datasets with sequence lengths comparable to the tile size, such as MNLI. For this dataset, Fig. 13 shows the relative execution times of three CORA implementations of AttnV—NoSplit, Split and Split-HFused—in which we progressively perform the two optimizations, on the Nvidia GPU and ARM CPU backends. On the GPU, operation splitting causes a slowdown despite lower wasted computation as it reduces parallelism, which is restored by hfusion. This is more apparent at lower batch sizes when there is amount of parallelism is lower. On the CPU, this drop in parallelism due to operation splitting does not cause a slowdown as the amount of hardware parallelism is much lower and so are the overheads of launching multiple kernels. Therefore, hfusion has no benefit in this case. We also evaluate these optimizations on the QK<sup>T</sup> operator in §D.6 in the appendix.

#### 7.4 Overheads in CORA

Let us now look at the overheads in CORA—the prelude code, the wasted computation due to partial padding and auxiliary data structure accesses in the generated code.

**Prelude Overheads:** The prelude code constructs the required auxiliary data structures (§5) and copies them to the accelerator's memory if needed. The table below lists the execution time (in ms) and memory (in kB) required for these tasks for a 6-layer transformer encoder on the GPU backend. It also shows the overheads associated with the storage lowering scheme used in past work we discussed in §5.2 (referred to as Sparse Storage in the table). As compared to this scheme, we see that CORA's specialized lowering scheme significantly reduces the resources required to compute the data structures associated with tensor storage. The overheads associated with loop fusion are higher than those associated with storage as we need to compute and store the relationship between all values of the fused and unfused loop iteration variables (§5.1). Copying the generated data structures to the GPU's memory is, however, the major source of the overhead. The overheads range from 0.7% (RACE dataset at batch size 128) to about 7% (CoLA dataset at batch size 32) of the total execution time of the encoder layer on the GPU. On the CPU, the overheads are a very small fraction of the execution times, because the execution times are much higher and because the memory copy costs are absent. We discuss some simple optimizations to reduce prelude overheads in §D.7 of the appendix.

| Dataset /<br>Batch Size | Sparse Storage<br>Time / Mem. | CoRA Storage<br>Time / Mem. | CoRa Loop Fusion<br>Time / Mem. | CoRa-<br>Copy |

|-------------------------|-------------------------------|-----------------------------|---------------------------------|---------------|

| CoLA / 32               | 0.09 / 267.97                 | 3.80e-03 / 2.93             | 5.35e-03 / 32.15                | Time          |

| CoLA / 128              | 0.35 / 1047.22                | 5.76e-03 / 11.18            | 0.02 / 104.22                   | 0.27          |

| RACE / 32               | 0.52 / 1607.97                | 4.15e-03 / 2.93             | 0.09 / 666.54                   | 0.42          |

| RACE / 128              | 2.02 / 6300.02                | 6.30e-03 / 11.18            | 0.34 / 2609.58                  | 0.99          |

**Partial Padding Overheads:** We saw that in CORA, small

amounts of padding can be specified for vloops (both unfused vloops and fused ones with bulk padding) and tensor storage to enable efficient code generation. While this leads to some wasted computation, we find that it is generally quite low. For the transformer encoder layer, we see a 3.5% increase in the amount of computation (computed analytically) over the ideal case without padding for a batch size of 32 and a 2.3% increase for a batch size of 128 across all the datasets evaluated. The overheads decrease with increasing batch size as bulk padding ensures that the sum of the sequence lengths in a batch is a multiple of a constant (64, in this case) irrespective of the batch size leading to a higher relative amount of padding at lower batch sizes. We provide further data and discussion in §D.7 of the appendix.

Ragged Tensor Overheads and Load Hoisting: CoRA's generated code accesses the auxiliary data structures generated by the prelude leading to frequent indirect memory accesses. We measure the overheads caused by these accesses for the operators used in MHA. While the data and more discussion are provided in §D.7, we note here that the indirect memory accesses do not cause any significant slowdown for the Proj1, Softmax, AttnV and the Proj2 operators. The accesses do lead to a higher slowdown in the QK<sup>T</sup> operator, which is the only operator where we fuse two vloops leading to complex memory access expressions. For this case, we find that hoisting data structures accesses outside loops when possible helps recover the lost performance.

## 8 RELATED WORK

Tensor Compilers: There has been extensive work on tensor compilers such as TVM (Chen et al., 2018a), Halide (Ragan-Kelley et al., 2013), Tiramisu (Baghdadi et al., 2019), Tensor Comprehensions (Vasilache et al., 2018), Fireiron (Hagedorn et al., 2020), Stripe (Zerrell & Bruestle, 2019), AKG (Zhao et al., 2021) as well as work by (Gysi et al., 2021) and (Bhaskaracharya et al., 2020) for dense tensors and Taco (Kjolstad et al., 2017), COMET (Tian et al., 2021) and (Hsu et al., 2021) for sparse tensors. This work has informed CoRA's design. We generalize the abstractions provided by dense tensor compilers to ragged tensors, while enabling efficient code generation for the latter. We saw that ragged tensors are similar to sparse tensors as both involve irregular storage. However, the degree of sparsity as well as properties of the applications they are used in differ significantly. CORA's specialized approach enables it to exploit these properties of ragged operators (e.g. insight I1 in §2) that past work cannot.<sup>9</sup>

Past work on DL compilers has also looked at handling dynamism. Nimble (Shen et al., 2020) develops dynamismaware compiler abstractions from the ground up. Its handling of shape dynamism is limited to variation across minibatches. CORA is therefore complementary to Nimble's techniques. Cortex (Fegade et al., 2021) handles recursive models by lowering the recursive control flow into sequential control flow on ragged tensors. CoRA can therefore potentially be used as part of its pipeline. CORA's use of uninterpreted functions and named dimensions has been inspired by their use in Cortex and past work on the Sparse Polyhedral Framework (Strout et al., 2018; Mohammadi et al., 2019; Nandy et al., 2018). Named dimensions are also similar to the index labels in COMET. CORA implements a limited form of the hfusion optimization, first proposed in (Li et al., 2020), as part of a tensor compiler.

DL Frameworks and Graph Optimizations: DL frameworks have recently begun adding support for ragged tensors with the RaggedTensor (TFR) class in TensorFlow and the NestedTensor (PTN) module for PyTorch. Very few operators are, however, supported for ragged tensors at this point (TFI; PTI). OCRA can be used to expand the set of ragged operators supported in these frameworks. CORA's techniques are complementary to graph optimizations for efficient DL execution such as data layout optimizations (Ivanov et al., 2020), kernel fusion (Zheng et al., 2020b) and operator scheduling (Ding et al., 2020) and can be used in conjunction with them.

Hand Optimized Implementations: There has been work on efficient implementations of certain important ragged tensor operations. This includes the work on variable-sized batched gemm operations (Li et al., 2019; Nath et al., 2010) as well as the work on Effective Transformers and Faster-Transformers, which we compared CORA's performance against in §7. This past work informs our work on CORA as we saw with the operator splitting transform in §4.1.

**Sparse Tensor Algebra:** There has been decades of past on work on efficient execution of sparse tensor operators. This work has been revisited recently in the context of DL by work on exploiting block sparsity in model weights (Gray et al.) as well as for tuning sparse kernels for the sparsity patterns and distributions usually encountered in DL (Gale et al., 2020). The thread remapping strategy discussed in §4.1 was implemented first in (Gale et al., 2020).

$<sup>^9</sup>$ We measured the performance of a few operators on triangular matrices implemented in Taco, a state-of-the-art sparse tensor compiler, using the CSR and blocked CSR formats. As seen in \$D.4, these implementations showed slowdowns ranging from  $1.33\times$  to  $95.37\times$  compared to the corresponding CoRA implementations.

<sup>&</sup>lt;sup>10</sup>Tensor contraction and similar operators such as batched gemm and convolution are generally not supported. PyTorch's NestedTensor further supports only a few elementwise and reduction operators (NTL) at this point.

## 9 CONCLUSION

This paper presented CORA, a tensor compiler for expressing and optimizing ragged operators to portably target CPUs and GPUs using simple and familiar abstractions. CORA's approach, specialized for ragged tensors, reduces overheads associated with techniques such as masking and padding. With DL being applied to an ever-increasing set of fields and the models getting more resource-intensive, we believe that efficiently handling the shape dynamism that naturally arises in many settings is important. CORA extends past work on tensor compilers by supporting efficient operators on ragged tensors. Our work can also be seen as a step towards unifying past work on sparse and dense tensor compilation. In the future, we plan to make CORA easier to use, potentially with the help of auto-scheduling techniques, and then to release CORA open source.

#### **ACKNOWLEDGMENTS**

This work was supported in part by grants from the National Science Foundation, Oracle and IBM, and by the Parallel Data Lab (PDL) Consortium (Amazon, Facebook, Google, Hewlett-Packard Enterprise, Hitachi, IBM, Intel, Microsoft, NetApp, Oracle, Pure Storage, Salesforce, Samsung, Seagate, TwoSigma and Western Digital). We would like to thank Saman Amarasinghe, Dominic Chen, Stephen Chou, Chris Fallin, Graham Neubig, Olatunji Ruwase as well as the Catalyst Research Group at Carnegie Mellon University for their suggestions and feedback on our work.

### REFERENCES

- Effective Transformer. URL https://github.com/bytedance/effective\_transformer. Last accessed Sept 09, 2021.

- FasterTransformer. URL https://github.com/ NVIDIA/FasterTransformer. Last accessed Sept 09, 2021.

- The nestedtensor package prototype: Readme.md. URL https://github.com/pytorch/nestedtensor/blob/master/nestedtensor/csrc/README.md. Last accessed Oct 15, 2021.

- OpenBLAS: An optimized BLAS library. URL https://www.openblas.net/. Last accessed Oct 08, 2021.

- NestedTensor Project Progress. URL https://github.com/pytorch/pytorch/issues/25032. Last accessed Oct 15, 2021.

- The nestedtensor package prototype. URL https://github.com/pytorch/nestedtensor. Last accessed Sept 09, 2021.

- Github issue: End2end transformer training by using ragged tensor. URL https://github.com/tensorflow/tensorflow/issues/40965.

Last accessed Oct 15, 2021.

- Ragged tensors. URL https://www.tensorflow.org/api\_docs/python/tf/RaggedTensor?version=nightly. Last accessed Sept 09, 2021.

- TorchScript. URL https://pytorch.org/docs/stable/jit.html. Last accessed Sept 09, 2021.

- Intel oneAPI Deep Neural Network Library. URL

https://software.intel.com/content/

www/us/en/develop/tools/oneapi/

components/onednn.html#gs.ah65z4. Last

accessed September 2, 2021.

- Everything you always wanted to know about padding and truncation, 2020. URL https://huggingface.co/transformers/v3.0.2/preprocessing.html#everything-you-always-wanted-to-know-about-padding-and-truncation. Last accessed Sept 22, 2021.

- Abadi, M., Barham, P., Chen, J., Chen, Z., Davis, A., Dean, J., Devin, M., Ghemawat, S., Irving, G., Isard, M., Kudlur, M., Levenberg, J., Monga, R., Moore, S., Murray, D. G., Steiner, B., Tucker, P., Vasudevan, V., Warden, P., Wicke, M., Yu, Y., and Zheng, X. TensorFlow: A system for large-scale machine learning. In *12th USENIX Symposium on Operating Systems Design and Implementation (OSDI 16)*, pp. 265–283, Savannah, GA, November 2016. USENIX Association. ISBN 978-1-931971-33-1. URL https://www.usenix.org/conference/osdi16/technical-sessions/presentation/abadi.

- Adams, A., Ma, K., Anderson, L., Baghdadi, R., Li, T.-M., Gharbi, M., Steiner, B., Johnson, S., Fatahalian, K., Durand, F., and Ragan-Kelley, J. Learning to optimize Halide with tree search and random programs. *ACM Trans. Graph.*, 38(4), July 2019. ISSN 0730-0301. doi: 10.1145/3306346.3322967. URL https://doi.org/10.1145/3306346.3322967.

- Baghdadi, R., Ray, J., Romdhane, M. B., Del Sozzo, E., Akkas, A., Zhang, Y., Suriana, P., Kamil, S., and Amarasinghe, S. Tiramisu: A polyhedral compiler for expressing fast and portable code. In *Proceedings of the 2019 IEEE/ACM International Symposium on Code Genera*tion and Optimization, CGO 2019, pp. 193–205. IEEE Press, 2019. ISBN 9781728114361.

- Bhaskaracharya, S. G., Demouth, J., and Grover, V. Automatic kernel generation for volta tensor cores. *CoRR*, abs/2006.12645, 2020. URL https://arxiv.org/abs/2006.12645.

- Briot, J., Hadjeres, G., and Pachet, F. Deep learning techniques for music generation A survey. *CoRR*, abs/1709.01620, 2017. URL http://arxiv.org/abs/1709.01620.

- Charara, A., Ltaief, H., and Keyes, D. Redesigning triangular dense matrix computations on gpus. In Dutot, P.-F. and Trystram, D. (eds.), *Euro-Par 2016: Parallel Processing*, pp. 477–489, Cham, 2016. Springer International Publishing. ISBN 978-3-319-43659-3.

- Chen, T., Moreau, T., Jiang, Z., Zheng, L., Yan, E., Shen, H., Cowan, M., Wang, L., Hu, Y., Ceze, L., Guestrin, C., and Krishnamurthy, A. TVM: An automated end-to-end optimizing compiler for deep learning. In *13th USENIX Symposium on Operating Systems Design and Implementation (OSDI 18)*, pp. 578–594, Carlsbad, CA, October 2018a. USENIX Association. ISBN 978-1-939133-08-3. URL https://www.usenix.org/conference/osdi18/presentation/chen.

- Chen, T., Zheng, L., Yan, E. Q., Jiang, Z., Moreau, T., Ceze, L., Guestrin, C., and Krishnamurthy, A. Learning to optimize tensor programs. *CoRR*, abs/1805.08166, 2018b. URL http://arxiv.org/abs/1805.08166.

- Chetlur, S., Woolley, C., Vandermersch, P., Cohen, J., Tran, J., Catanzaro, B., and Shelhamer, E. cuDNN: Efficient primitives for deep learning. *CoRR*, abs/1410.0759, 2014. URL http://arxiv.org/abs/1410.0759.

- Chou, S., Kjolstad, F., and Amarasinghe, S. Format abstraction for sparse tensor algebra compilers. *Proc. ACM Program. Lang.*, 2(OOPSLA), October 2018. doi: 10.1145/3276493. URL https://doi.org/10.1145/3276493.

- Conneau, A., Rinott, R., Lample, G., Williams, A., Bowman, S. R., Schwenk, H., and Stoyanov, V. Xnli: Evaluating cross-lingual sentence representations. In *Proceedings* of the 2018 Conference on Empirical Methods in Natural Language Processing. Association for Computational Linguistics, 2018.

- De Moura, L. and Bjørner, N. Z3: An efficient SMT solver. In *International conference on Tools and Algorithms for the Construction and Analysis of Systems*, pp. 337–340. Springer, 2008.

- Devlin, J., Chang, M., Lee, K., and Toutanova, K. BERT: pre-training of deep bidirectional transformers for language understanding. *CoRR*, abs/1810.04805, 2018. URL http://arxiv.org/abs/1810.04805.

- Ding, Y., Zhu, L., Jia, Z., Pekhimenko, G., and Han, S. IOS: inter-operator scheduler for CNN acceleration. *CoRR*, abs/2011.01302, 2020. URL https://arxiv.org/abs/2011.01302.

- Dolan, W. B. and Brockett, C. Automatically constructing a corpus of sentential paraphrases. In *Proceedings* of the Third International Workshop on Paraphrasing (IWP2005), 2005. URL https://aclanthology.org/I05-5002.

- Fegade, P., Chen, T., Gibbons, P., and Mowry, T. Cortex: A compiler for recursive deep learning models. In Smola, A., Dimakis, A., and Stoica, I. (eds.), *Proceedings of Machine Learning and Systems*, volume 3, pp. 38–54, 2021. URL https://proceedings.mlsys.org/paper/2021/file/182be0c5cdcd5072bb1864cdee4d3d6e-Paper.pdf.

- Gale, T., Zaharia, M., Young, C., and Elsen, E. *Sparse GPU Kernels for Deep Learning*. IEEE Press, 2020. ISBN 9781728199986.

- Gray, S., Radford, A., and Kingma, D. P. Gpu kernels for block-sparse weights. URL https://cdn.openai.com/blocksparse/blocksparsepaper.pdf.

- Gysi, T., Müller, C., Zinenko, O., Herhut, S., Davis, E., Wicky, T., Fuhrer, O., Hoefler, T., and Grosser, T. Domain-specific multi-level ir rewriting for gpu: The open earth compiler for gpu-accelerated climate simulation. *ACM Trans. Archit. Code Optim.*, 18(4), September 2021. ISSN 1544-3566. doi: 10.1145/3469030. URL https://doi.org/10.1145/3469030.

- Hagedorn, B., Elliott, A. S., Barthels, H., Bodik, R., and Grover, V. Fireiron: A data-movement-aware scheduling language for gpus. In *Proceedings of the ACM International Conference on Parallel Architectures and Compilation Techniques*, PACT '20, pp. 71–82, New York, NY, USA, 2020. Association for Computing Machinery. ISBN 9781450380751. doi: 10.1145/3410463.3414632. URL https://doi.org/10.1145/3410463.3414632.

- He, K., Zhang, X., Ren, S., and Sun, J. Deep residual learning for image recognition. In 2016 IEEE Conference on Computer Vision and Pattern Recognition (CVPR), pp. 770–778, 2016. doi: 10.1109/CVPR.2016.90.

- Hsu, O., Yadav, R., Chou, S., Olukotun, K., Amarasinghe, S., and Kjolstad, F. Compilation of sparse array programming models. 2021.

- Huang, C. A., Vaswani, A., Uszkoreit, J., Shazeer, N., Hawthorne, C., Dai, A. M., Hoffman, M. D., and Eck, D. An improved relative self-attention mechanism for transformer with application to music generation. *CoRR*, abs/1809.04281, 2018. URL http://arxiv.org/ abs/1809.04281.

- Ivanov, A., Dryden, N., Ben-Nun, T., Li, S., and Hoefler, T. Data movement is all you need: A case study on optimizing transformers. *CoRR*, abs/2007.00072, 2020. URL https://arxiv.org/abs/2007.00072.

- Jain, P., Jain, A., Nrusimha, A., Gholami, A., Abbeel, P., Gonzalez, J., Keutzer, K., and Stoica, I. Checkmate: Breaking the memory wall with optimal tensor rematerialization. In Dhillon, I., Papailiopoulos, D., and Sze, V. (eds.), *Proceedings of Machine Learning and Systems*, volume 2, pp. 497–511, 2020. URL https://proceedings.mlsys.org/paper/2020/file/084b6fbb10729ed4da8c3d3f5a3ae7c9-Paper.pdf.

- Kirisame, M., Lyubomirsky, S., Haan, A., Brennan, J., He, M., Roesch, J., Chen, T., and Tatlock, Z. Dynamic tensor rematerialization. In *International Conference on Learning Representations*, 2021. URL https://openreview.net/forum?id=Vfs\_2RnODOH.

- Kjolstad, F., Kamil, S., Chou, S., Lugato, D., and Amarasinghe, S. The tensor algebra compiler. *Proc. ACM Program. Lang.*, 1(OOPSLA):77:1–77:29, October 2017. ISSN 2475-1421. doi: 10.1145/3133901. URL http://doi.acm.org/10.1145/3133901.

- Lai, G., Xie, Q., Liu, H., Yang, Y., and Hovy, E. RACE: Large-scale ReAding comprehension dataset from examinations. In *Proceedings of the 2017 Conference on Empirical Methods in Natural Language Processing*, pp. 785–794, Copenhagen, Denmark, September 2017. Association for Computational Linguistics. doi: 10.18653/v1/D17-1082. URL https://aclanthology.org/D17-1082.

- Li, A., Zheng, B., Pekhimenko, G., and Long, F. Automatic horizontal fusion for GPU kernels. *CoRR*, abs/2007.01277, 2020. URL https://arxiv.org/abs/2007.01277.

- Li, X., Liang, Y., Yan, S., Jia, L., and Li, Y. A coordinated tiling and batching framework for efficient gemm on gpus. In *Proceedings of the 24th Symposium on Principles and Practice of Parallel Programming*, PPoPP '19, pp. 229–241, New York, NY, USA, 2019. Association for Computing Machinery. ISBN 9781450362252. doi: 10.1145/3293883.3295734. URL https://doi.org/10.1145/3293883.3295734.

- Mohammadi, M. S., Cheshmi, K., Dehnavi, M. M., Venkat, A., Yuki, T., and Strout, M. M. Extending index-array properties for data dependence analysis. In Hall, M. and Sundar, H. (eds.), *Languages and Compilers for Parallel Computing*, pp. 78–93, Cham, 2019. Springer International Publishing. ISBN 978-3-030-34627-0.

- Mullapudi, R. T., Adams, A., Sharlet, D., Ragan-Kelley, J., and Fatahalian, K. Automatically scheduling halide image processing pipelines. *ACM Trans. Graph.*, 35 (4), July 2016. ISSN 0730-0301. doi: 10.1145/2897824.2925952. URL https://doi.org/10.1145/2897824.2925952.

- Nandy, P., Hall, M., Davis, E. C., Olschanowsky, C., Mohammadi, M. S., He, W., and Strout, M. Abstractions for specifying sparse matrix data transformations. In *Proceedings of the Eighth International Workshop on Polyhedral Compilation Techniques*, 2018.

- Nath, R., Tomov, S., and Dongarra, J. An improved magma gemm for fermi graphics processing units. *The International Journal of High Performance Computing Applications*, 24(4):511–515, 2010. doi: 10.1177/1094342010385729. URL https://doi.org/10.1177/1094342010385729.

- Paszke, A., Gross, S., Massa, F., Lerer, A., Bradbury, J., Chanan, G., Killeen, T., Lin, Z., Gimelshein, N., Antiga, L., Desmaison, A., Kopf, A., Yang, E., DeVito, Z., Raison, M., Tejani, A., Chilamkurthy, S., Steiner, B., Fang, L., Bai, J., and Chintala, S. PyTorch: An imperative style, high-performance deep learning library. In Wallach, H., Larochelle, H., Beygelzimer, A., d'Alché-Buc, F., Fox, E., and Garnett, R. (eds.), Advances in Neural Information Processing Systems 32, pp. 8024–8035. Curran Associates, Inc., 2019. URL http://papers.neurips.cc/paper/9015-pytorch-an-imperative-style-high-performance-deep-learning-library.pdf.

- Ragan-Kelley, J., Barnes, C., Adams, A., Paris, S., Durand, F., and Amarasinghe, S. Halide: A language and compiler for optimizing parallelism, locality, and recomputation in image processing pipelines. In *Proceedings of the 34th ACM SIGPLAN Conference on Programming Language Design and Implementation*, PLDI '13, pp. 519–530, New York, NY, USA, 2013. Association for Computing Machinery. ISBN 9781450320146. doi: 10.1145/2491956.2462176. URL https://doi.org/10.1145/2491956.2462176.

- Rajpurkar, P., Jia, R., and Liang, P. Know what you don't know: Unanswerable questions for squad. *CoRR*, abs/1806.03822, 2018. URL http://arxiv.org/abs/1806.03822.

- Shen, H., Roesch, J., Chen, Z., Chen, W., Wu, Y., Li, M., Sharma, V., Tatlock, Z., and Wang, Y. Nimble: Efficiently compiling dynamic neural networks for model inference. arXiv preprint arXiv:2006.03031, 2020. URL https://arxiv.org/abs/2006.03031.

- Singh, S., Steiner, B., Hegarty, J., and Leather, H. Using graph neural networks to model the performance of deep neural networks, 2021.

- Smith, S. and Karypis, G. Tensor-matrix products with a compressed sparse tensor. In *Proceedings of the 5th Workshop on Irregular Applications: Architectures and Algorithms*, IA;sup¿3;/sup¿ '15, New York, NY, USA, 2015. Association for Computing Machinery. ISBN 9781450340014. doi: 10.1145/2833179.2833183. URL https://doi.org/10.1145/2833179.2833183.

- Strout, M. M., Hall, M., and Olschanowsky, C. The sparse polyhedral framework: Composing compiler-generated inspector-executor code. *Proceedings of the IEEE*, 106 (11):1921–1934, 2018.

- Tai, K. S., Socher, R., and Manning, C. D. Improved semantic representations from tree-structured long short-term memory networks. arXiv preprint arXiv:1503.00075, 2015.

- Tian, R., Guo, L., Li, J., Ren, B., and Kestor, G. A high-performance sparse tensor algebra compiler in multi-level IR. *CoRR*, abs/2102.05187, 2021. URL https://arxiv.org/abs/2102.05187.

- van den Oord, A., Dieleman, S., Zen, H., Simonyan, K., Vinyals, O., Graves, A., Kalchbrenner, N., Senior, A. W., and Kavukcuoglu, K. Wavenet: A generative model for raw audio. *CoRR*, abs/1609.03499, 2016. URL http://arxiv.org/abs/1609.03499.

- Vasilache, N., Zinenko, O., Theodoridis, T., Goyal, P., De-Vito, Z., Moses, W. S., Verdoolaege, S., Adams, A., and Cohen, A. Tensor comprehensions: Framework-agnostic high-performance machine learning abstractions. arXiv preprint arXiv:1802.04730, 2018.

- Vaswani, A., Shazeer, N., Parmar, N., Uszkoreit, J., Jones, L., Gomez, A. N., Kaiser, L., and Polosukhin, I. Attention is all you need. *CoRR*, abs/1706.03762, 2017. URL http://arxiv.org/abs/1706.03762.

- Warstadt, A., Singh, A., and Bowman, S. R. Neural network acceptability judgments. *Transactions of the Association for Computational Linguistics*, 7:625–641, March 2019. doi: 10.1162/tacl\_a\_00290. URL https://aclanthology.org/Q19-1040.

- Williams, A., Nangia, N., and Bowman, S. A broad-coverage challenge corpus for sentence understanding through inference. In Proceedings of the 2018 Conference of the North American Chapter of the Association for Computational Linguistics: Human Language Technologies, Volume 1 (Long Papers), pp. 1112–1122, New

- Orleans, Louisiana, June 2018. Association for Computational Linguistics. doi: 10.18653/v1/N18-1101. URL https://aclanthology.org/N18-1101.

- Yang, Z., Dai, Z., Yang, Y., Carbonell, J. G., Salakhutdinov, R., and Le, Q. V. Xlnet: Generalized autoregressive pretraining for language understanding. *CoRR*, abs/1906.08237, 2019. URL http://arxiv.org/abs/1906.08237.

- Zerrell, T. and Bruestle, J. Stripe: Tensor compilation via the nested polyhedral model. *CoRR*, abs/1903.06498, 2019. URL http://arxiv.org/abs/1903.06498.

- Zhao, J., Li, B., Nie, W., Geng, Z., Zhang, R., Gao, X., Cheng, B., Wu, C., Cheng, Y., Li, Z., Di, P., Zhang, K., and Jin, X. Akg: Automatic kernel generation for neural processing units using polyhedral transformations. In *Proceedings of the 42nd ACM SIGPLAN International Conference on Programming Language Design and Implementation*, PLDI 2021, pp. 1233–1248, New York, NY, USA, 2021. Association for Computing Machinery. ISBN 9781450383912. doi: 10.1145/3453483.3454106. URL https://doi.org/10.1145/3453483.3454106.

- Zheng, L., Jia, C., Sun, M., Wu, Z., Yu, C. H., Haj-Ali, A., Wang, Y., Yang, J., Zhuo, D., Sen, K., Gonzalez, J. E., and Stoica, I. Ansor: Generating high-performance tensor programs for deep learning. In *14th USENIX Symposium on Operating Systems Design and Implementation (OSDI 20)*, pp. 863–879. USENIX Association, November 2020a. ISBN 978-1-939133-19-9. URL https://www.usenix.org/conference/osdi20/presentation/zheng.

- Zheng, Z., Zhao, P., Long, G., Zhu, F., Zhu, K., Zhao, W., Diao, L., Yang, J., and Lin, W. Fusionstitching: Boosting memory intensive computations for deep learning workloads. *CoRR*, abs/2009.10924, 2020b. URL https://arxiv.org/abs/2009.10924.

## **APPENDIX**

We now look at additional details regarding CORA's mechanism in §A, §B and §C, and discuss further aspects of the evaluation in §D. Notably, we look at how CORA can exploit masking in masked MHA to obtain further savings in §D.3, discuss how CORA's overheads are quite low, allowing it to effectively exploit raggedness (§D.7) and look more closely at CORA's performance on the transformer model and where the benefits come from in §D.8.

## A RAGGED API

## A.1 Thread Remapping Policy

We discussed, in §4, that CORA allows users to specify a thread remapping policy to influence how iterations of a parallel loop are scheduled on the execution units in the hardware substrate. This is illustrated in Fig 14.

## **B** RAGGED API LOWERING

## **B.1** Tensor Storage Lowering

In §5.2, we briefly discussed the storage lowering schemes used by past work on sparse tensor compilers and by CORA. Both are illustrated in Fig. 15 and discussed more below.

**Sparse Storage Access Lowering Scheme Used in Past Work:** Recall the 4-dimensional attention tensor X we discussed in §5.2 and is illustrated again in Fig. 15. We saw that the first and the third dimensions of X are cdims and correspond to the batch size  $(s_1)$  and the number of attention heads  $(s_3)$  respectively. The other two dimensions, which correspond to sequence lengths are vdims. For X, the size of a slice for both these vdims is the same function  $(s_{24}())$  of the outermost batch dimension.

Figure 14. Thread remapping allows users to influence the scheduling of iterations to allow for better load balancing.

The sparse tensor compiler Taco (Kjolstad et al., 2017), the performance of which look at in §D.4, uses a tree-

based modular scheme (first proposed in the work (Smith & Karypis, 2015) on the Compressed Sparse Fiber tensor format) to model sparse tensor storage. In this scheme, illustrated in Fig. 15 for tensor X, tensor storage is modeled as hierarchical tree structure, where each tensor dimension corresponds to a tree level. Note that this tree abstraction exists only at compile time. As mentioned before, this scheme assumes that the number of non-zeros in a slice of a sparse tensor dimension can depend on the indices of all outer dimensions in general. We saw that this is not the case with ragged tensors and that this is the source of sub-optimality in this lowering scheme for the applications we look at. Because every slice may have a different number of non-zero elements, when used to store a ragged tensor, this storage scheme would store auxiliary data proportional to the number of slices for a given vdim. For our example tensor X in Fig. 15, the outer of the two vdims (the second dimension) has  $s_1$  slices while the number of slices in the inner vdim (the fourth dimension) is  $s_3 \sum_{i=0}^{s_1} s_{24}(i)$ . Therefore, the amount of auxiliary data computed and stored would be equal to  $s_1 + s_3 \sum_{i=0}^{s_1} s_{24}(i)$ , which as we saw in §7.4 can be much larger than CORA's specialized scheme.

## Algorithm 1 Procedure to lower ragged tensor accesses

```

1: procedure LOWERACCESS([b_1, ..., b_n])

offset \leftarrow 0

2:

relaxed \leftarrow [b_1, ..., b_n]

3:

\triangleright Compute D_i(\overrightarrow{B_{\leq i}})

4:

for i \leftarrow n to 1 do

5:

D \leftarrow 1

if O_G(i) \neq \emptyset then

6:

7:

D \leftarrow A_i(relaxed[j])

8:

9:

D \leftarrow relaxed[i]

10:

end if

11:

for j in S(i) - \{i\} do

if O_G(j) \neq \emptyset then

12:

D \leftarrow D * A_j(relaxed[j])

13:

14:

15:

D \leftarrow D * s_j(relaxed[I_G(j)])

16:

end if

17:

end for

18:

relaxed[i] \leftarrow s_i(relaxed[I_G(i)])

19:

offset \leftarrow offset + D

20:

end for

21:

return offset

22: end procedure

```

**CORA's Storage Access Lowering Scheme:** We saw that CORA's storage access lowering scheme is specialized for ragged tensors and enables us to reduce the amount of auxiliary data that needs to be computed as compared to the

scheme used by past work while allowing O(1) accesses to ragged tensor storage. In order to enable O(1) tensor accesses, we essentially need to compute a memory offset within a constant number of operations. The reason sparse tensor formats such as the CSR format do not allow constant time tensor accesses is because they explicitly store indices of one or more dimensions along with every non-zero value. Thus, given a tensor index, one needs to perform a search over these indices to obtain the correct non-zero element. In the case of ragged tensors, however, we note that within a vdim slice, the data in densely packed with no intervening zero elements. Therefore, we can get away without storing explicit indices for any dimension. The auxiliary data structures that CoRA's lowering scheme computes only store memory offsets using arrays which we can access and add up the memory offsets in constant time. Below, we describe exactly how these data structures are computed and how they are used to lower memory accesses.

Let T be an n-dimensional tensor with dimensions numbered 1 to n such that dimension 1 is the outermost dimension. Given a tensor access  $T(b_1,..,b_n)$ , we need to generate a flat memory offset  $Off_T(b_1,..,b_n)$  to access T.

Given a tensor and its corresponding storage layout, we define what we refer to as the dimension graph or dgraph for short (Fig. 15). The dgraph G of the n-dimensional tensor T is a pair (D, E) where D is the set of all dimensions  $\{1,...,n\}$  and E is a set of directed edges. An edge  $d_1 \rightarrow d_2$ belongs to E if the size of a slice of dimension  $d_2$  depends on the index  $b_{d_1}$  in the tensor access  $T(b_1,..,b_n)$ . Thus, a cdim will not have any incoming edge in the dgraph, while a vdim would. It also follows, for example, that the outermost dimension of the tensor, which is always a cdim, will not have any incoming edges. More generally, we note that the dgraph of a given tensor is always acyclic as the size of a slice of a given vdim depends only on the indices of outer dimensions. Further, given a dimension d, let  $O_G(d) =$  $\{d_2|(d,d_2)\in E\}$  and  $I_G(d)=\{d_1|(d_1,d)\in E\}$  be the set of outgoing and incoming dimensions, respectively, for d in the dimension graph. The size of a slice of a vdim d can now be written as  $s_d(I_G(d))$ . For cdims, this quantity is constant. Let  $O_G^*(d)$  denote the transitive closure of  $O_G(d)$ . Also, let  $O_G^{ex}(d) = O_G(d) - \bigcup_{i \in O_G(d)} O_G^*(i)$ .