#### Flash based Caching: Opportunities and Challenges

Nisha Talagala, Swami Sundararaman

Copyright © 2013 Fusion-io, Inc. All rights reserved.

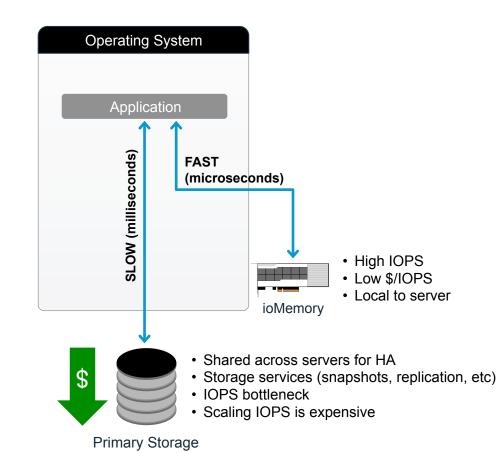

# Why Flash Caching?

- IOPS closer to application

- Read from cache; write to primary storage

FUSION-iO

- No need to reconfigure storage or applications

- Preserve application mobility

- Reduce storage costs

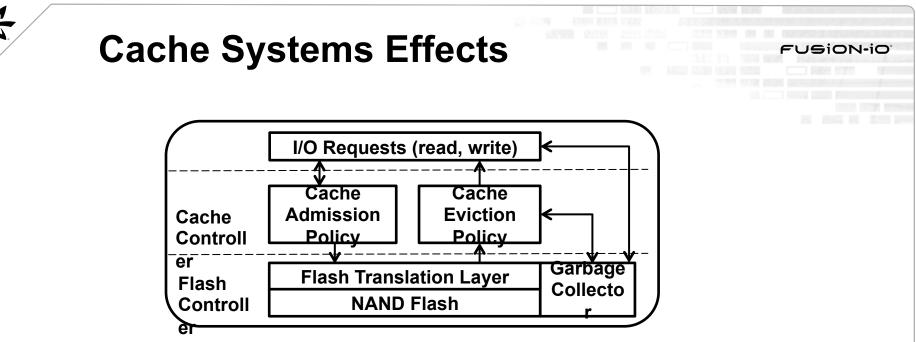

# **Flash Caches are Different**

- Flash caches are different

- Higher write pressures than their storage counterparts

- Admitted read-misses are writes, writes are writes

- Writes (misses, write through) have endurance and performance cost in garbage collection

- Cache pollution has hit rate costs; endurance and additional performance costs in flash caches

- The workload presented to flash devices are write intensive

- Smaller cache size suffers from even higher CLWA (7x-8x)

- CLWA: Cache Layer Write Amplification

| Original Writes | Cache Size (GB) | Cache Writes (GB) | CLWA       | Hit Rate |

|-----------------|-----------------|-------------------|------------|----------|

| 36.8            | 80              | 322.13            | 8.75       | 14.03    |

|                 | 100             | 300.11            | 8.16       | 20.67    |

|                 | 120             | 275.83            | 7.5        | 27.98    |

|                 |                 | May 47, 2042      | $\bigcirc$ |          |

TPC-Backup: cache layer write-amplification under ADMIT\_ALL

#### Agenda

- Cache workload impacts on flash

- Reducing cache and flash layer write amplification

- Memory efficiency in cache algorithms

- Write back caches

- Cache filters and intelligence

- Futures

## **Multiplicative Write Amplification**

FUSION-10

|                          |                     |                          | $ \land $         |                          |      | $\bigcap$ |            |                 |

|--------------------------|---------------------|--------------------------|-------------------|--------------------------|------|-----------|------------|-----------------|

| Original Writes<br>(GiB) | Cache<br>Size (GiB) | Cache<br>Writes<br>(GiB) | GC Writes<br>(GiB | Total<br>Writes<br>(GiB) | CLWA | FLWA      | Multiplier | Hit Rate<br>(%) |

| 36.8                     | 120                 | 275.83                   | 1352.01           | 1627.84                  | 7.5  | 5.9       | 44.25      | 27.98           |

|                          | 100                 | 300.11                   | 1459.13           | 1759.24                  | 8.16 | 5.86      | 47.82      | 20.67           |

|                          | 80                  | 322.13                   | 1553.98           | 1876.11                  | 8.75 | 5.82      | 50.93      | 14.03           |

more writes due to 'miss'

Even more writes due to garbage collection

Collective impact: CLWA \* FLWA

# **Improving Flash Cache Endurance**

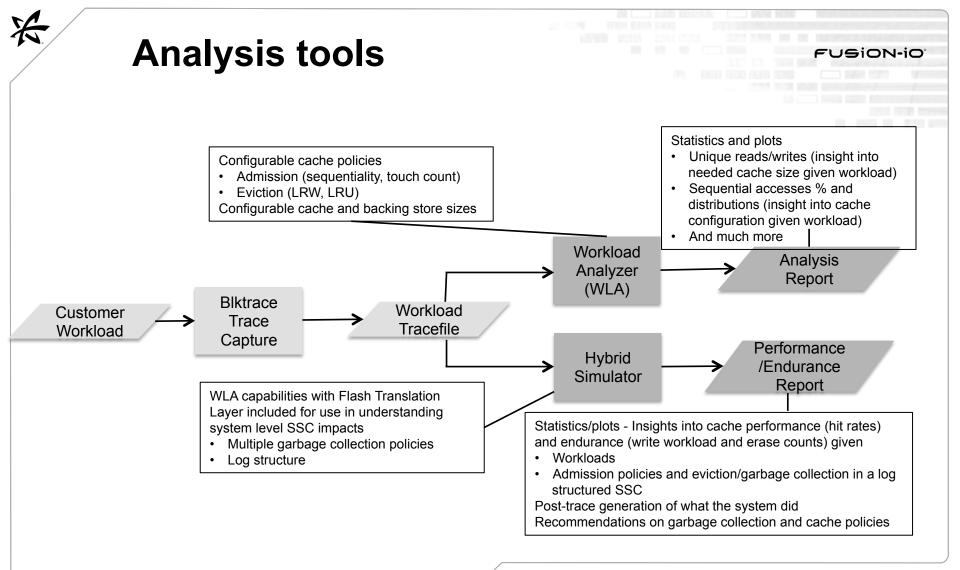

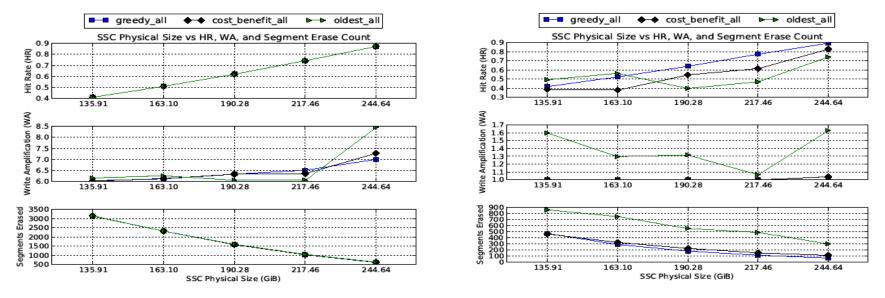

- What are the workload characteristics that a flashbased cache is likely to encounter ?

- How do different cache admission and eviction policies affect read cache hit rate and write workload ?

- How do various garbage collection strategies impact writes and erases to media ?

- What combination of admission control polices, eviction policies, and garbage collection strategies can be used to improve hit rates while reducing writes to the solid state cache (SSC) ?

High Endurance flash-based cache characteristics are influenced by

- User workloads

- System reserve capacity

- Garbage collection strategies (e.g. victim segment selection policy (tail drop) runs risk of cleaning recently used data thus increased read misses and increased write load)

- Cache admission policies (e.g. directly impacts write workload when read misses)

- Cache eviction policies (e.g. can impact write workload when eviction of recently used)

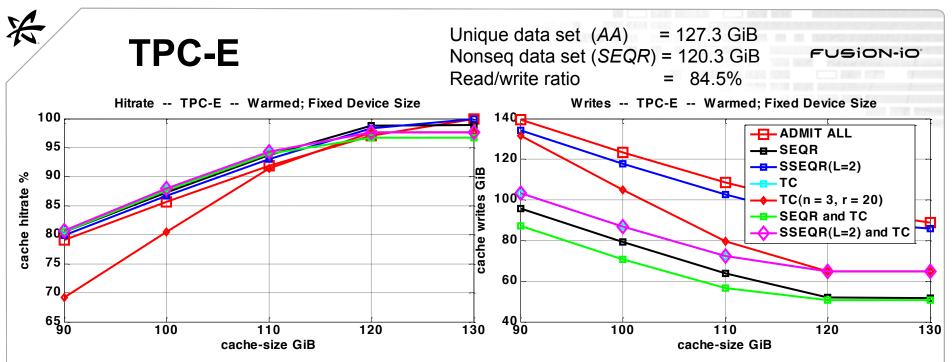

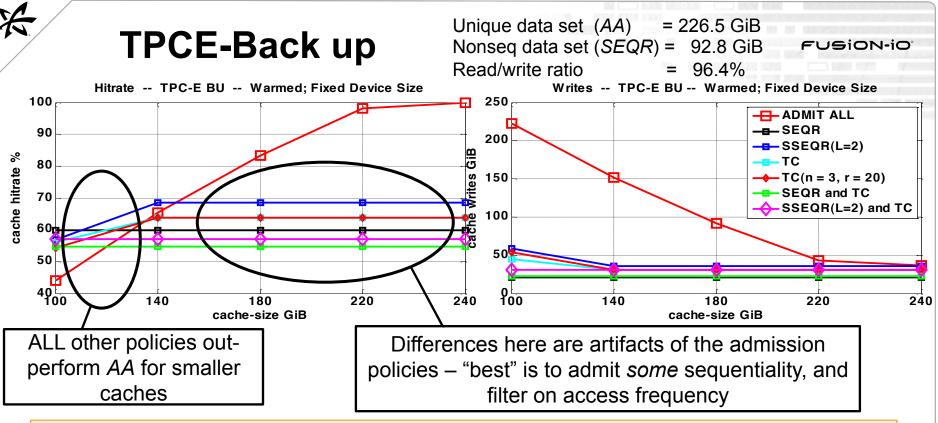

Tpce-with backup workload

#### Reducing Flash Layer Write Amplification

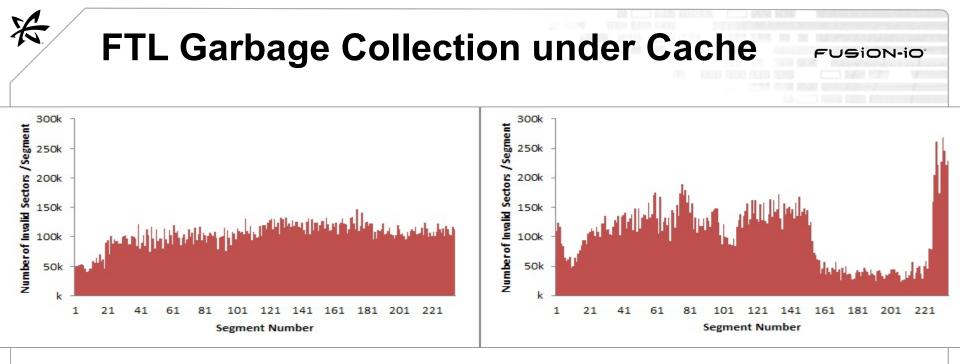

#### Cache-based eviction

GC-based eviction

Cache based eviction vs Garbage Collection based eviction

- Invalidity distribution differs depending on cache algorithm

- Renders Flash based GC less efficient

### **Combined effects**

#### FUSION-10

| Admit all   | Origina |

|-------------|---------|

| Tail drop   | (0      |

| Cache-based | 3       |

| eviction    |         |

|             |         |

| Admit all<br>Tail drop                         | Original Writes<br>(GiB) | s Cache<br>Size (GiB | Writes<br>(GiB)          | GC Writes<br>(GiB | Writes<br>(GiB)          | CLWA                | FLWA                | Multiplier | Hit Rate<br>(%) |

|------------------------------------------------|--------------------------|----------------------|--------------------------|-------------------|--------------------------|---------------------|---------------------|------------|-----------------|

| Cache-based                                    | 36.8                     | 120                  | 275.83                   | 1352.01           | 1627.84                  | 7.5                 | 5.9                 | 44.25      | 27.98           |

| eviction                                       |                          | 100                  | 300.11                   | 1459.13           | 1759.24                  | 8.16                | 5.86                | 47.82      | 20.67           |

|                                                |                          | 80                   | 322.13                   | 1553.98           | 1876.11                  | 8.75                | 5.82                | 50.93      | 14.03           |

|                                                |                          |                      |                          |                   |                          |                     |                     |            |                 |

| sequentiality +<br>touch count<br>Cost-benefit | Original<br>Writes (GiB) | Cache<br>Size (GiB)  | Cache<br>Writes<br>(GiB) | GC Writes<br>(GiB | Total<br>Writes<br>(GiB) | CLWA                | FLWA                | Multiplier | Hit Rate<br>(%) |

| touch count                                    | -                        |                      | Writes                   |                   | Writes                   | <b>CLWA</b><br>1.02 | <b>FLWA</b><br>2.19 | Multiplier |                 |

| touch count<br>Cost-benefit                    | Writes (GiB)             | Size (GiB)           | Writes<br>(GiB)          | (GiB              | Writes<br>(GiB)          |                     |                     |            | (%)             |

Total

Reduced WA (CLWA, FLWA) by over 10x

Improved hit rate for small – mid cache sizes

Cache

# **Observations**

- More write-intensive from a flash point of view

- Increasing cache size provides improvement but at cost

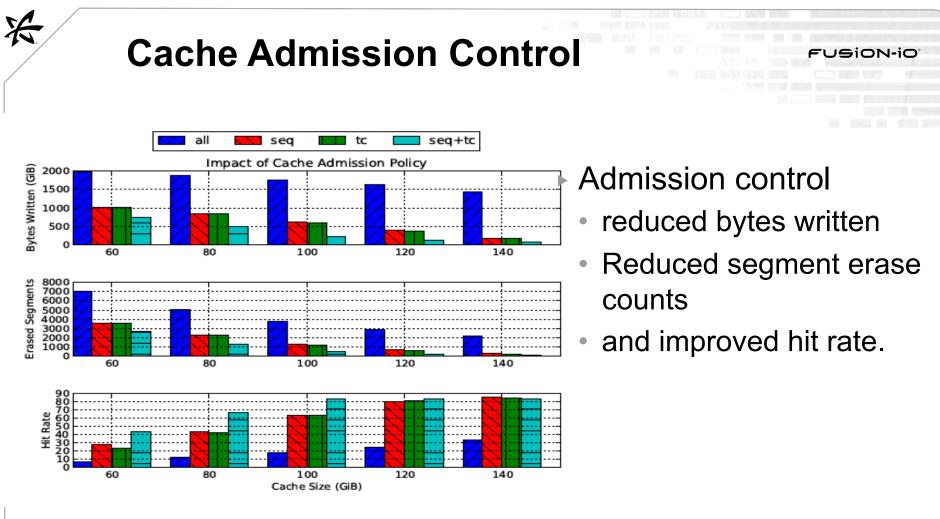

- Admission control can reduce CLWA

- Eviction control can reduce FLWA

- Cache-based eviction is not optimal

- Use of capacity reservation guarantees QoS on hit rate

- At the expense of FLWA.

FUSION-IO

## Agenda

- Cache workload impacts on flash

- Reducing cache and flash layer write amplification

- Memory efficiency in cache algorithms

- Write back caches

- Cache filters and intelligence

- App level caches

- Futures

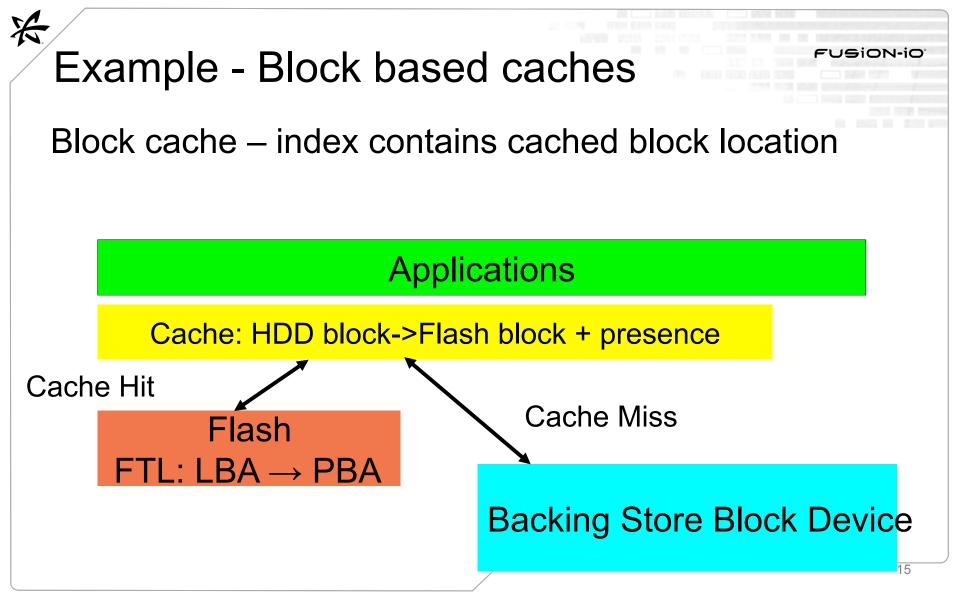

FUSION-iO

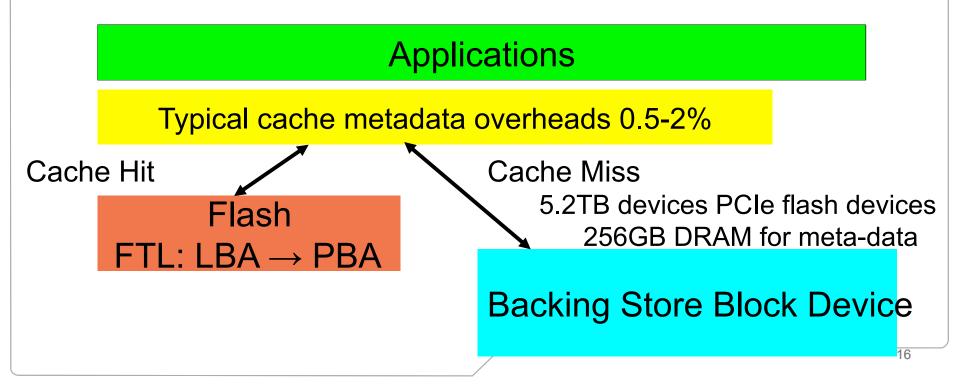

Mapping required to translate disk locations to flash locations – overhead per flash block, per disk block

FUSION-IO

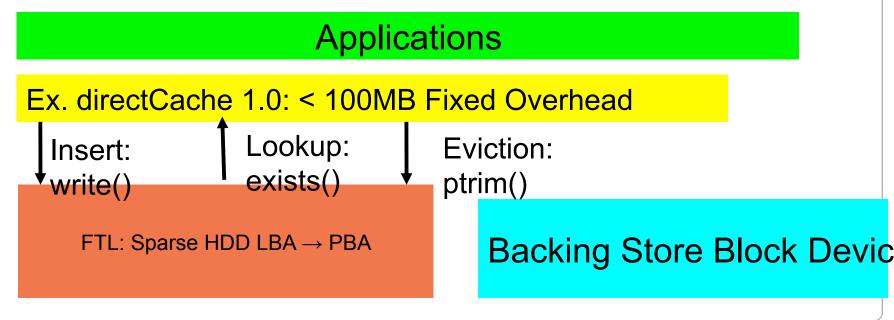

# Reduced Metadata Caches

Leverage FTL mapping and dynamic allocation Enables "zero metadata" caches – fixed metadata cost

# **Memory Efficient Admission Policies**

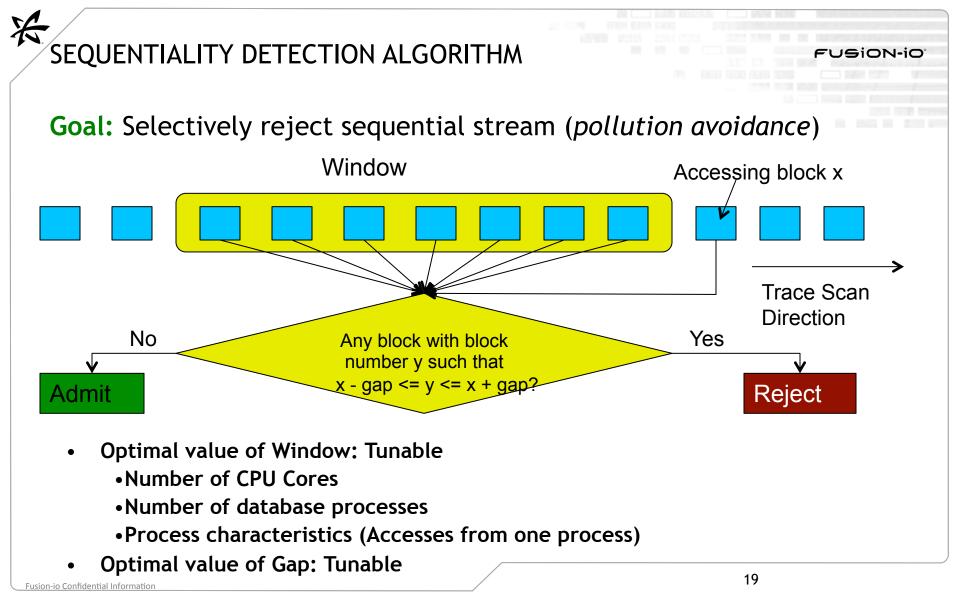

- SEQuentiality Rejection: SEQR

- Parameters: window size and gap

- Selective SEQuentiality Rejection: SSEQR(L = x)

- Additional parameter: admitted sequential lengths, x MB

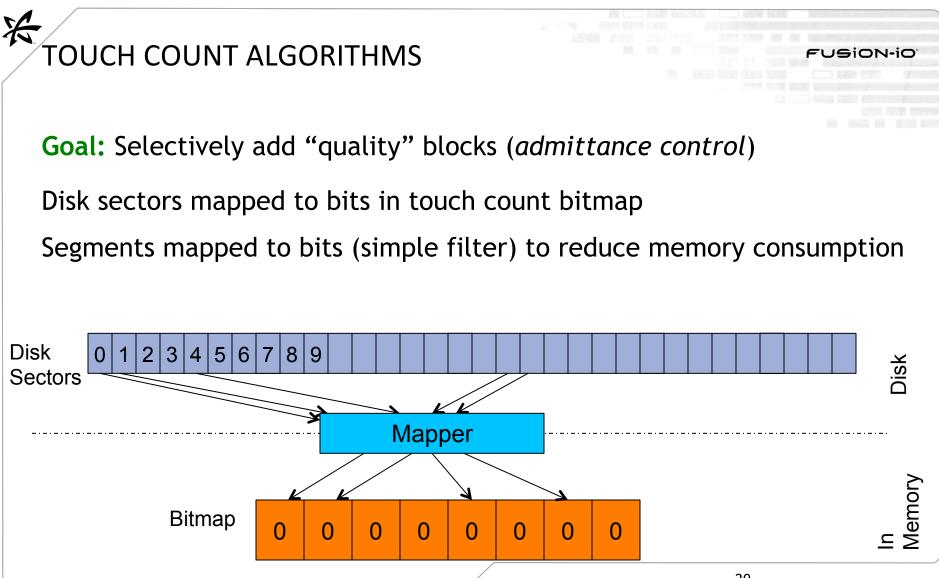

- ► Touch Count: *TC*

- Parameters: touch-count segment length, bits per segment, threshold, bitmap count, bitmap rotation mechanism.

- ► SEQR + TC

- ► SSEQR + TC

AA vs. SEQR: 2% HR reduction; 64% write reduction

- Larger cache leads to increased hit-rate and fewer writes

- Depends on workload and policies in effect!

- More restrictive admission policies have comparable hit-rates with greatly reduced writes

- More restrictive admission policies perform better (hit-rate) than ADMIT ALL for smaller cache sizes, without consideration to writes

- Great discrepancies present for GiB > 140 are due to smaller critical cache sizes of restrictive admission policies AND great sequential scans

- More restrictive admission policies perform better (hit-rate wise) than ADMIT ALL (for sub-critical cache sizes), with 375% reduction in writes

- In presence of additional pollution, the admission policy is VERY important to reduce writes

### Agenda

- Cache workload impacts on flash

- Reducing cache and flash layer write amplification

- Memory efficiency in cache algorithms

- Write back caches

- Cache filters and intelligence

- Futures

FUSION-iO

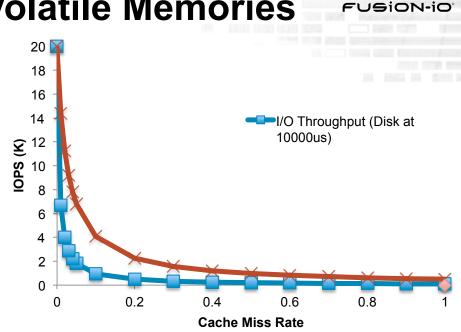

# Data Tiering for Non-Volatile Memories

- Flash is valuable as cache, but even small miss rates result in significant performance loss

- Write back cache policies provide high hit rate, but can result in incoherent back end storage state at failure

- Enable write back caching with coherent back end state

- Ordered write back

- Journaled write back

- Journaled write back with application provided consistency hints

- Provides improved performance over write through with consistency guarantees

Write Policies for Host Side Flash Caches. R. Koller\*, L. Marmol\*, R. Rangaswami\*, S. Sundararaman+, N. Talagala+, M Zhao\*. FAST 2013.

<u>https://www.usenix.org/conference/fast13/write-policies-host-side-flash-caches</u>

\*Florida International University, +Fusion-io

- Write Policies for Host Side Flash Caches. FAST 2013

- R. Koller\*, L. Marmol\*, R. Rangaswami\*, S. Sundararaman+, N. Talagala+, M Zhao\*

- \* Florida International University, +Fusion-io

https://www.usenix.org/conference/fast13/write-policies-host-side-flash-caches

#### Improving Endurance of High Performance Flash-based Cache Devices. SYSTOR 2013

\*

J. Yang, N. Plasson, G. Gillis, N. Talagala, S. Sundararaman, R. Wood

Fusion-io

►

Camera-ready copy to be available soon

- Admission Polices for Solid State Cache Devices. NVM Workshop 2013

- G. Gillis, S. Sundararaman, N. Talagala, A. Mudrankit, J. Ludwig

Fusion-io

http://nvmw.ucsd.edu/2013/assets/abstracts/56

# **Intelligent Caching with Controls**

- Fusion-io ioTurbine software addresses FILE, VOLUME and DISK I/O

- Write through caching: Transparent and non-disruptive to I/O path

- Intercepts storage calls

- Closest to the application, in the guest OS (workload specific)

- Caches the Active Working Set; most active data is cached

- Allow storage to write data more efficiently

- Selective cache control

- Control which files, volumes, or disks should be cached

| Pagefile.sys 🗹           | Database redo 🗷 |

|--------------------------|-----------------|

| Mirrored volume <b>1</b> | Kernel32.dll ☑  |

#### **Futures**

- QoS in cache operating well with FTLs

- Cache sharing

- New memories

#### THANK YOU

fusionio.com | REDEFINE WHAT'S POSSIBLE