AN INFORMAL PUBLICATION FROM ACADEMIA'S PREMIERE STORAGE SYSTEMS RESEARCH CENTER DEVOTED TO ADVANCING THE STATE OF THE ART IN STORAGE AND INFORMATION INFRASTRUCTURES.

# CONTENTS

| DeltaFS I                  |

|----------------------------|

| Director's Letter2         |

| Year in Review4            |

| Recent Publications5       |

| PDL News & Awards8         |

| 3Sigma 12                  |

| Defenses & Proposals 14    |

| Alumni News 18             |

| New PDL Faculty & Staff 19 |

|                            |

# PDL CONSORTIUM MEMBERS

Alibaba Group Broadcom, Ltd. Dell EMC Facebook Google Hewlett Packard Enterprise Hitachi, Ltd. IBM Research Intel Corporation Micron Microsoft Research MongoDB NetApp, Inc. Oracle Corporation Salesforce Samsung Information Systems America Seagate Technology Toshiba Two Sigma Veritas Western Digital

# Massive Indexed Directories in DeltaFS

by Qing Zheng, George Amvrosiadis & the DeltaFS Group

Faster storage media, faster interconnection networks, and improvements in systems software have significantly mitigated the effect of I/O bottlenecks in HPC applications. Even so, applications that read and write data in small chunks are limited by the ability of both the hardware and the software to handle such workloads efficiently. Often, scientific applications partition their output using one file per process. This is a problem on HPC computers with hundreds of thousands of cores and will only worsen with exascale computers, which will be an order of magnitude larger. To avoid wasting time creating output files on such machines, scientific applications are forced to use libraries that combine multiple I/O streams into a single file. For many applications where output is produced out-of-order, this must be followed by a costly, massive data sorting operation. DeltaFS allows applications to write to an arbitrarily large number of files, while also guaranteeing efficient data access without requiring sorting.

The first challenge when handling an arbitrarily large number of files is dealing with the resulting metadata load. We manage this using the transient and serverless DeltaFS file system [I]. The transient property of DeltaFS allows each program that uses it to individually control the amount of computing resources dedicated to the file system, effectively scaling metadata performance under application control. When combined with DeltaFS's serverless nature, file system design and provisioning decisions are decoupled from the overall design of the HPC platform. As a result, applications that create one file for each process are no longer tied to the platform storage system's ability to handle metadata-heavy workloads. The HPC platform can also provide scalable file creation rates without requiring a fundamental redesign of the platform's storage system.

The second challenge is guaranteeing both fast writing and reading for workloads that consist primarily of small I/O transfers. This work was inspired by interactions with cosmologists seeking to explore the trajectories of the highest energy particles in an astrophysics simulation using the VPIC plasma simulation code [2]. VPIC is a highly-

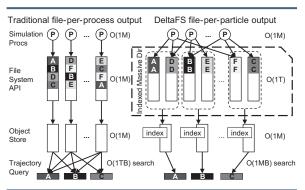

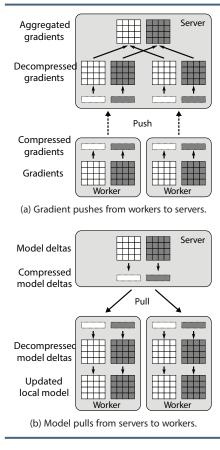

Figure 1: DeltaFS in-situ indexing of particle data in an Indexed Massive Directory. While indexed particle data are exposed as one DeltaFS subfile per particle, they are stored as indexed log objects in the underlying storage.

optimized particle simulation code developed at Los Alamos National Laboratory (LANL). Each VPIC simulation proceeds in timesteps, and each process represents a bounding box in the physical simulation space that particles move through. Every few timesteps the simulation stops, and each process creates a file and writes the data for the particles that are currently located within its bounding box. This is the default, file-per-process

# FROM THE DIRECTOR'S CHAIR GREG GANGER

Hello from fabulous Pittsburgh!

25 years! This past fall, we celebrated 25 years of the Parallel Data Lab. Started by Garth after he defended his PhD dissertation on RAID at UC-Berkeley, PDL has

seen growth and success that I can't imagine he imagined... from the early days of exploring new disk array approaches to today's broad agenda of large-scale storage and data center infrastructure research... from a handful of core CMU researchers and industry participants to a vibrant community of scores of CMU researchers and 20 sponsor companies. Amazing.

It has been another great year for the Parallel Data Lab, and I'll highlight some of the research activities and successes below. Others, including graduations, publications, awards, etc., can be found throughout the newsletter. But, I can't not start with the biggest PDL news item of this 25th anniversary year: Garth has graduated;). More seriously, 25 years after founding PDL, including guiding/ nurturing it into a large research center with sustained success (25 years!), Garth decided to move back to Canada and take the reins (as President and CEO) of the new Vector Institute for AI. We wish him huge success with this new endeavor! Garth has been an academic role model, a mentor, and a friend to me and many others... we will miss him greatly, and he knows that we will always have a place for him at PDL events.

Because it overlaps in area with Vector, I'll start my highlighting of PDL activities with our continuing work at the intersection for machine learning (ML) and systems. We continue to explore new approaches to system support for large-scale machine learning, especially aspects of how ML systems should adapt and be adapted in cloud computing environments. Beyond our earlier focus on challenges around dynamic resource availability and time-varying resource interference, we continue to explore challenges related to training models over geo-distributed data, training very large models, and how edge resources should be shared among inference applications using DNNs for video stream processing. We are also exploring how ML can be applied to make systems better, including even ML systems ;).

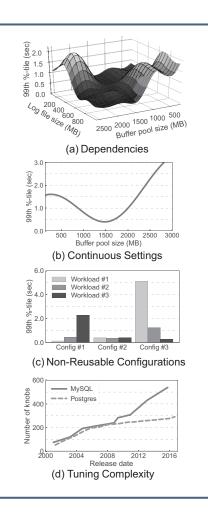

Indeed, much of PDL's expansive database systems research activities center on embedding automation in DBMSs. With an eye toward simplifying administration and improving performance robustness, there are a number of aspects of Andy's overall vision of a self-driving database system being explored and realized. To embody them, and other ideas, a new open source DBMS called Peloton has been created and is being continuously enhanced. There also continue to be cool results and papers on better exploitation of NVM in databases, improved concurrency control mechanisms, and range query filtering. I thoroughly enjoy watching (and participating) in the great energy that Andy has infused into database systems research at CMU.

Of course, PDL continues to have a big focus on storage systems research at various levels. At the high end, PDL's long-standing focus on metadata scaling for scalable storage has led to continued research into benefits of and approaches to allowing important applications to manage their own namespaces and metadata for periods of time. In addition to bypassing traditional metadata bottlenecks

# THE PDL PACKET

#### THE PARALLEL DATA LABORATORY

School of Computer Science Department of ECE Carnegie Mellon University 5000 Forbes Avenue Pittsburgh, PA 15213-3891 voice 412•268•6716 FAX 412•268•3010

#### PUBLISHER

Greg Ganger

#### EDITOR

Joan Digney

The PDL Packet is published once per year to update members of the PDL Consortium. A pdf version resides in the Publications section of the PDL Web pages and may be freely distributed. Contributions are welcome.

#### THE PDL LOGO

Skibo Castle and the lands that comprise its estate are located in the Kyle of Sutherland in the northeastern part of Scotland. Both 'Skibo' and 'Sutherland' are names whose roots are from Old Norse, the language spoken by the Vikings who began washing ashore regularly in the late ninth century. The word 'Skibo' fascinates etymologists, who are unable to agree on its original meaning. All agree that 'bo' is the Old Norse for 'land' or 'place,' but they argue whether 'ski' means 'ships' or 'peace' or 'fairy hill.'

Although the earliest version of Skibo seems to be lost in the mists of time, it was most likely some kind of fortified building erected by the Norsemen. The present-day castle was built by a bishop of the Roman Catholic Church. Andrew Carnegie, after making his fortune, bought it in 1898 to serve as his summer home. In 1980, his daughter, Margaret, donated Skibo to a trust that later sold the estate. It is presently being run as a luxury hotel.

#### PARALLEL DATA LABORATORY

#### FACULTY

Greg Ganger (PDL Director) 412•268•1297 ganger@ece.cmu.edu George Amvrosiadis Seth Copen Goldstein David Andersen Mor Harchol-Balter Lujo Bauer Gauri Joshi Nathan Beckmann Todd Mowry Daniel Berger Onur Mutlu Chuck Cranor Priya Narasimhan David O'Hallaron Lorrie Cranor Christos Faloutsos Andy Pavlo Kawon Fatabalian Majd Sakr Rajeev Gandhi M. Satyanarayanan Saugata Ghose Srinivasan Seshan Phil Gibbons Rashmi Vinayak Garth Gibson Hui Zhang

#### STAFF MEMBERS

Bill Courtright, 412 • 268 • 5485 (PDL Executive Director) wcourtright@cmu.edu Karen Lindenfelser, 412 • 268 • 6716 (PDL Administrative Manager) karen@ece.cmu.edu Jason Boles Joan Digney Chad Dougherty Mitch Franzos Alex Glikson Charlene Zang

#### VISITING RESEARCHERS / POST DOCS

Rachata Ausavarungnirun Kazuhiro Saito Hyeontaek Lim

#### **GRADUATE STUDENTS**

| Abutalib Aghayev<br>Joy Arulraj<br>Ben Blum | Conglong Li<br>Kunmin Li<br>Yang Li |

|---------------------------------------------|-------------------------------------|

| V. Parvathi Bhogaraju                       | Yixin Luo                           |

| Amirali Boroumand                           | Lin Ma                              |

| Sol Boucher                                 | Diptesh Majumdar                    |

| Christopher Canel                           | Ankur Mallick                       |

| Dominic Chen                                | Charles McGuffey                    |

| Haoxian Chen                                | Prashanth Menon                     |

| Malhar Chaudhari                            | Yuqing Miao                         |

| Andrew Chung                                | Wenqi Mou                           |

| Chris Fallin                                | Pooja Nilangekar                    |

| Pratik Fegade                               | Yiqun Ouyang                        |

| Ziqiang Feng                                | Jun Woo Park                        |

| Samarth Gupta                               | Aurick Qiao                         |

| Aaron Harlap                                | Souptik Sen                         |

| Kevin Hsieh                                 | Sivaprasad Sudhir                   |

| Fan Hu                                      | Aaron Tian                          |

| Abhilasha Jain                              | Dana Van Aken                       |

| Saksham Jain                                | Nandita Vijaykumar                  |

| Angela Jiang                                | Haoran Wang                         |

| Ellango Jothimurugesan                      | Jianyu Wang                         |

| Saurabh Arun Kadekodi                       | Justin Wang                         |

| Anuj Kalia                                  | Ziqi Wang                           |

| Rajat Kateja                                | Jinliang Wei                        |

| Jin Kyu Kim                                 | Daniel Wong                         |

| Thomas Kim                                  | Lin Xiao                            |

| Vamshi Konagari                             | Hao Zhang                           |

| Jack Kosaian                                | Huanchen Zhang                      |

| Marcel Kost                                 | Qing Zheng                          |

| Michael Kuchnik                             | Giulio Zhou                         |

|                                             |                                     |

# FROM THE DIRECTOR'S CHAIR

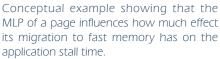

entirely during the heaviest periods of activity, this approach promises opportunities for efficient in-situ index creation to enable fast queries for subsequent analysis activities. At the lower end, we continue to explore how software systems should be changed to maximize the value from NVM storage, including addressing read-write performance asymmetry and providing storage management features (e.g., page-level checksums, dedup, etc.) without yielding load/store efficiency. We're excited about continuing to work with PDL companies on understanding where storage hardware is (and should be) going and how it should be exploited in systems.

PDL continues to explore questions of resource scheduling for cloud computing, which grows in complexity as the breadth of application and resource types grow. Our cluster scheduling research continues to explore how job runtime estimates can be automatically generated and exploited to achieve greater efficiency. Our most recent work explores more robust ways of exploiting imperfectly-estimated runtime information, finding that providing full distributions of likely runtimes (e.g., based on history of "similar" jobs) works quite well for real-world workloads as reflected in real cluster traces. We are also exploring scheduling for adaptively-sized "virtual clusters" within public clouds, which introduces new questions about which machine types to allocate, how to pack them, and how aggressively to release them.

I continue to be excited about the growth and evolution of the storage systems and cloud classes created and led by PDL faculty — their popularity is at an all-time high again this year. These project-intensive classes prepare IOOs of MS students to be designers and developers for future infrastructure systems. They build FTLs that store real data (in a simulated NAND Flash SSD), hybrid cloud file systems that work, cluster schedulers, efficient ML model training apps, etc. It's really rewarding for us and for them. In addition to our lectures and the projects, these classes each feature 3-5 corporate guest lecturers (thank you, PDL Consortium members!) bringing insight on real-world solutions, trends, and futures.

Many other ongoing PDL projects are also producing cool results. For example, to help our (and others') file systems research, we have developed a new file system aging suite, called Geriatrix. Our key-value store research continues to expose new approaches to indexing and remote value access. This newsletter and the PDL website offer more details and additional research highlights.

I'm always overwhelmed by the accomplishments of the PDL students and staff, and it's a pleasure to work with them. As always, their accomplishments point at great things to come.

The CMU fence displays a farewell message to Garth.

# May 2018

- 20th annual Spring Visit Day.

- Qing Zheng and Michael Kuchnik will be interning with LANL this summer.

### April 2018

- Andy Pavlo receive the 2018 Joel & Ruth Spira Teaching Award.

- Lorrie Cranor received the IAPP Leadership Award.

- Srinivasan Seshan was appointed Head of he Computer Science Dept. at CMU.

- Michael Kuchnik received an NDSEG Fellowship for his work on machine learning in HPC systems.

- Huanchen Zhang proposed his PhD research "Towards Space-Efficient High-Performance In-Memory Search Structures."

- Jun Woo Park presented "3Sigma: Distribution-based Cluster Scheduling for Runtime Uncertainty" at EuroSys '18 in Porto, Portugal.

- Charles McGuffey delivered his speaking skills talk on "Designing Algorithms to Tolerate Processor Faults."

- Qing Zheng gave his speaking skills talk "Light-Weight In-Situ Indexing For Scientific Workloads."

#### March 2018

Andy Pavlo wins Google Faculty Research Award for his research

Greg Ganger and PDL alums Hugo Patterson (Datrium) and Jiri Schindler (HPE) enjoy social time at the PDL Retreat.

on automatic database management systems.

- Anuj Kalia proposed his thesis research "Efficient Networked Systems for Datacenter Fabrics with RPCs."

- Nathan Beckmann presented "LHD: Improving Cache Hit Rate by Maximizing Hit Density" at NSDI '18 in Renton, WA.

- Rajat Kateja presented "Viyojit: Decoupling Battery and DRAM Capacities for Battery-Backed DRAM" at NVMW '18 in San Diego, CA.

- Rachata Ausavarungnirun presented "MASK: Redesigning the GPU Memory Hierarchy to Support Multi-Application Concurrency" at ASPLOS'18 in Williamsburg, VA.

- ASPLOS'18 in Williamsburg, VA.

#### February 2018

- Lorrie Cranor wins top SIG-CHI Award, given to individuals who promote the application of human-computer interaction research to pressing social needs.

- Six posters were presented at the Ist SysML Conference at Stanford U. on various work related to creating more efficient systems for machine learning.

- Yixin Luo successfully defended his PhD dissertation on "Architectural Techniques for Improving NAND Flash Memory Reliability."

- Andy Pavlo awarded a Sloan Fellowship to continue his work on the study of database management systems, specifically main memory systems, non-relational systems (NoSQL), transaction processing systems (NewSQL) and large-scale data analytics.

#### December 2017

Mor Harchol-Balter and Onur Mutlu were made Fellows of the ACM. Mor was selected "for contributions to performance modeling and analysis of distributed computing systems." Onur, who is now at ETH Zurich, was chosen for "contributions to computer architecture research, especially in memory systems."

- Joy Arulraj proposed his PhD research "The Design & Implementation of a Non-Volatile Memory Database Management System."

- Dana Van Aken gave her speaking skills talk on "Automatic Database Management System Tuning Through Large-scale Machine Learning."

### November 2017

Qing Zheng presented "Software-Defined Storage for Fast Trajectory Queries using a DeltaFS Indexed Massive Directory" at PDSW-DISCS '17 in Denver, CO.

### October 2017

- Lorrie Cranor awarded FORE Systems Chair of Computer Science.

- Qing Zheng gave his speaking skills talk on "Light-weight In-situ Analysis with Frugal Resource Usage."

- Rachata Ausavarungnirun presented "Mosaic: A GPU Memory Manager with Application-Transparent Support for Multiple Page Sizes" and Vivek Seshadri presented Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology" at MICRO '17 in Cambridge, MA.

- Timothy Zhu presented "Workload Compactor: Reducing Datacenter Cost while Providing Tail Latency SLO Guarantees" at SoCC'17 in Santa Clara, CA.

- ✤ 25th annual PDL Retreat.

# September 2017

- Garth Gibson to lead new Vector Institute for AI in Toronto.

- Hongyi Xin delivered his speaking skills talk on "Improving DNA Read Mapping with Error-resilient Seeds."

# Geriatrix: Aging what you see and what you don't see. A file system aging approach for modern storage systems

Saurabh Kadekodi, Vaishnavh Nagarajan, Gregory R. Ganger & Garth A. Gibson

2018 USENIX Annual Technical Conference (ATC'18). July 11–13, 2018, Boston, MA.

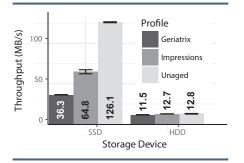

File system performance on modern primary storage devices (Flash-based SSDs) is greatly affected by aging of the free space, much more so than were mechanical disk drives. We introduce Geriatrix, a simple-to-use profile driven file system aging tool that induces target levels of fragmentation in both allocated files (what you see) and remaining free space (what you don't see), unlike previous approaches that focus on just the former. This paper describes and evaluates the effectiveness of Geriatrix, showing that it recreates both fragmentation effects better than previous approaches. Using Geriatrix, we show that measurements presented in many recent file systems papers are higher than should be expected, by up to 30% on mechanical

Aging impact on Ext4 atop SSD and HDD. The three bars for each device represent the FS freshly formatted (unaged), aged with Geriatrix, and aged with Impressions. Although relatively small differences are seen with the HDD, aging has a big impact on FS performance on the SSD. Although their file fragmentation levels are similar, the higher free space fragmentation produced by Geriatrix induces larger throughput reductions than for Impressions. (HDD) and up to 75% on Flash (SSD) disks. Worse, in some cases, the performance rank ordering of file system designs being compared are different from the published results.

Geriatrix will be released as open source software with eight built-in aging profiles, in the hopes that it can address the need created by the increased performance impact of file system aging in modern SSD-based storage.

# A Case for Packing and Indexing in Cloud File Systems

Saurabh Kadekodi, Bin Fan, Adit Madan, Garth A. Gibson & Gregory R. Ganger

10th USENIX Workshop on Hot Topics in Cloud Computing. July 9, 2018, Boston, MA.

Tiny objects are the bane of highly scalable cloud object stores. Not only do tiny objects cause massive slowdowns, but they also incur tremendously high costs due to current operation-based pricing models. For example, in Amazon S3's current pricing scheme, uploading IGB data by issuing tiny (4KB) PUT requests (at 0.0005 cents each) is approximately 57x more expensive than storing that same IGB for a month. To address this problem, we propose client-side packing of files into gigabyte-sized blobs with embedded indices to identify each file's location. Experiments with a packing implementation in Alluxio (an open-source distributed file system) illustrate the potential benefits, such as simultaneously increasing file creation throughput by up to 61x and decreasing cost by over 99.99%.

# SOAP: One Clean Analysis of All Age-Based Scheduling Policies

Ziv Scully, Mor Harchol-Balter & Alan Scheller-Wolf

Proceedings of ACM SIGMETRICS 2018 Conference on Measurement

and Modeling of Computer Systems Los Angeles, CA, June 2018.

We consider an extremely broad class of M/G/I scheduling policies called SOAP: Schedule Ordered by Agebased Priority. The SOAP policies include almost all scheduling policies in the literature as well as an infinite number of variants which have never been analyzed, or maybe not even conceived. SOAP policies range from classic policies, like first-come, first-serve (FCFS), foreground-background (FB), class-based priority, and shortest remaining processing time (SRPT); to much more complicated scheduling rules, such as the famously complex Gittins index policy and other policies in which a job's priority changes arbitrarily with its age. While the response time of policies in the former category is well understood, policies in the latter category have resisted response time analysis. We present a universal analysis of all SOAP policies, deriving the mean and Laplace-Stieltjes transform of response time.

# Towards Optimality in Parallel Job Scheduling

Ben Berg, Jan-Pieter Dorsman & Mor Harchol-Balter

Proceedings of ACM SIGMETRICS 2018 Conference on Measurement and Modeling of Computer Systems Los Angeles, CA, June 2018.

To keep pace with Moore's law, chip designers have focused on increasing the number of cores per chip rather than single core performance. In turn, modern jobs are often designed to run on any number of cores. However, to effectively leverage these multi-core chips, one must address the question of how many cores to assign to each job. Given that jobs receive sublinear speedups from additional cores, there is an obvious tradeoff: allocating more cores to an individual job reduces the job's runtime, but in turn decreases

#### continued from page 5

the efficiency of the overall system. We ask how the system should schedule jobs across cores so as to minimize the mean response time over a stream of incoming jobs.

To answer this question, we develop an analytical model of jobs running on a multi-core machine. We prove that EQUI, a policy which continuously divides cores evenly across jobs, is optimal when all jobs follow a single speedup curve and have exponentially distributed sizes. EQUI requires jobs to change their level of parallelization while they run. Since this is not possible for all workloads, we consider a class of "fixed-width" policies, which choose a single level of parallelization, k, to use for all jobs. We prove that, surprisingly, it is possible to achieve EQUI's performance without requiring jobs to change their levels of parallelization by using the optimal fixed level of parallelization, k\*. We also show how to analytically derive the optimal k\* as a function of the system load, the speedup curve, and the job size distribution.

In the case where jobs may follow different speedup curves, finding a good scheduling policy is even more challenging. In particular, we find that policies like EQUI which performed well in the case of a single speedup function now perform poorly. We propose a very simple policy, GREEDY\*, which performs near-optimally when compared to the numerically-derived optimal policy.

## 3Sigma: Distribution-based Cluster Scheduling for Runtime Uncertainty

Jun Woo Park, Alexey Tumanov, Angela Jiang, Michael A. Kozuch & Gregory R. Ganger

EuroSys '18, April 23–26, 2018, Porto, Portugal. Supersedes CMU-PDL-17-107, Nov. 2017.

The 3Sigma cluster scheduling system uses job runtime histories in a new way. Knowing how long each job will

execute enables a scheduler to more effectively pack jobs with diverse time concerns (e.g., deadline vs. thesooner-the-better) and placement preferences on heterogeneous cluster resources. But, existing schedulers use single-point estimates (e.g., mean or median of a relevant subset of historical runtimes), and we show that they are fragile in the face of real-world estimate error profiles. In particular, analysis of job traces from three different large-scale cluster environments shows that, while the runtimes of many jobs can be predicted well, even state-of-the-art predictors have wide error profiles with 8-23% of predictions off by a factor of two or more. Instead of reducing relevant history to a single point, 3Sigma schedules jobs based on full distributions of relevant runtime histories and explicitly creates plans that mitigate the effects of anticipated runtime uncertainty. Experiments with workloads derived from the same traces show that 3Sigma greatly outperforms a state-of-the-art scheduler that uses point estimates from a state-of-the-art predictor; in fact, the performance of 3Sigma approaches the end-to-end performance of a scheduler based on a hypothetical, perfect runtime predictor. 3Sigma reduces SLO miss rate, increases cluster goodput, and improves or matches latency for best effort jobs.

# LHD: Improving Cache Hit Rate by Maximizing Hit Density

Nathan Beckmann, Haoxian Chen & Asaf Cidon

15th USENIX Symposium on Networked Systems Design and Implementation (NSDI 18). April 9–11, 2018, Renton, WA.

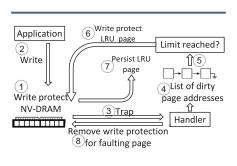

Cloud application performance is heavily reliant on the hit rate of datacenter key-value caches. Key-value caches typically use least recently used (LRU) as their eviction policy, but LRU's hit rate is far from optimal under real workloads. Prior research

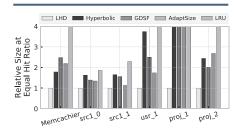

Relative cache size needed to match LHD's hit rate on different traces. LHD requires roughly one-fourth of LRU's capacity, and roughly half of that of prior eviction policies.

has proposed many eviction policies that improve on LRU, but these policies make restrictive assumptions that hurt their hit rate, and they can be difficult to implement efficiently.

We introduce least hit density (LHD), a novel eviction policy for key-value caches. LHD predicts each object's expected hits-per-spaceconsumed (hit density), filtering objects that contribute little to the cache's hit rate. Unlike prior eviction policies, LHD does not rely on heuristics, but rather rigorously models objects' behavior using conditional probability to adapt its behavior in real time.

To make LHD practical, we design and implement RankCache, an efficient key-value cache based on memcached. We evaluate RankCache and LHD on commercial memcached and enterprise storage traces, where LHD consistently achieves better hit rates than prior policies. LHD requires much less space than prior policies to match their hit rate, on average 8X less than LRU and 2-3X less than recently proposed policies. Moreover, RankCache requires no synchronization in the common case, improving request throughput at 16 threads by 8 over LRU and by 2X over CLOCK.

continued on page 7

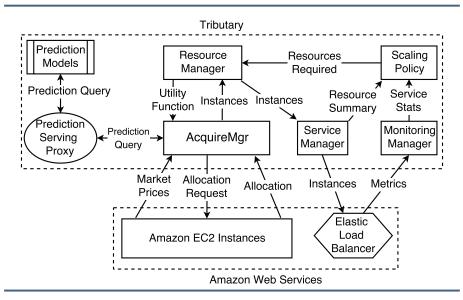

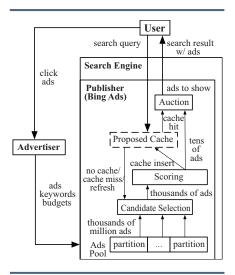

## Tributary: Spot-dancing for Elastic Services with Latency SLOs

Aaron Harlap, Andrew Chung, Alexey Tumanov, Gregory R. Ganger & Phillip B. Gibbons

Carnegie Mellon University Parallel Data Lab Technical Report CMU-PDL-18-102, Jan. 2018.

The Tributary elastic control system embraces the uncertain nature of transient cloud resources, such as AWS spot instances, to manage elastic services with latency SLOs more robustly and more cost-effectively. Such resources are available at lower cost, but with the proviso that they can be preempted en masse, making them risky to rely upon for business-critical services. Tributary creates models of preemption likelihood and exploits the partial independence among different resource offerings, selecting collections of resource allocations that will satisfy SLO requirements and adjusting them over time as client workloads change. Although Tributary's collections are often larger than required in the absence of preemptions, they are cheaper because of both lower spot costs and partial refunds for preempted resources. At the same time, the often-larger sets allow unexpected workload bursts to be handled without SLO violation. Over a range of web service workloads, we find that Tributary reduces cost for achieving a given SLO by 81–86% compared to traditional scaling on non-preemptible resources and by 47–62% compared to the high-risk approach of the same scaling with spot resources.

# MLtuner: System Support for Automatic Machine Learning Tuning

Henggang Cui, Gregory R. Ganger & Phillip B. Gibbons

arXiv:1803.07445vI [cs.LG] 20 Mar, 2018.

MLtuner automatically tunes settings for training tunables — such as the learning rate, the momentum, the mini-batch size, and the data staleness bound—that have a significant impact on large-scale machine learning (ML) performance. Traditionally, these tunables are set manually, which is unsurprisingly error prone and difficult to do without extensive domain knowledge. MLtuner uses efficient snapshotting, branching, and optimization-guided online trial-and-error to find good initial settings as well as

The Tributary Architecture.

to re-tune settings during execution. Experiments show that MLtuner can robustly find and re-tune tunable settings for a variety of ML applications, including image classification (for 3 models and 2 datasets), video classification, and matrix factorization. Compared to state-of-the-art ML auto-tuning approaches, MLtuner is more robust for large problems and over an order of magnitude faster.

#### Addressing the Long-Lineage Bottleneck in Apache Spark

Haoran Wang, Jinliang Wei & Garth Gibson

Carnegie Mellon University Parallel Data Lab Technical Report CMU-PDL-18-101, January 2018.

Apache Spark employs lazy evaluation [II, 6]; that is, in Spark, a dataset is represented as Resilient Distributed Dataset (RDD), and a single-threaded application (driver) program simply describes transformations (RDD to RDD), referred to as lineage [7, 12], without performing distributed computation until output is requested. The lineage traces computation and dependency back to external (and assumed durable) data sources, allowing Spark to opportunistically cache intermediate RDDs, because it can recompute everything from external data sources. To initiate computation on worker machines, the driver process constructs a directed acyclic graph (DAG) representing computation and dependency according to the requested RDD's lineage. Then the driver broadcasts this DAG to all involved workers requesting they execute their portion of the result RDD. When a requested RDD has a long lineage, as one would expect from iterative convergent or streaming applications [9, 15], constructing and broadcasting computational dependencies can become a significant bottleneck. For example, when solving matrix factorization using Gemulla's iterative convergent

## April 2018 Andy Pavlo Receives 2018 Joel & Ruth Spira Teaching Award

The School of Computer Science honored outstanding faculty and staff members April 5 during the annual Founder's Day ceremony

in Rashid Auditorium. It was the seventh year for the event and was hosted by Dean Andrew Moore. Andy Pavlo, Assistant Professor in the Computer Science Department (CSD), was the winner of the Joel and Ruth Spira Teaching Award, sponsored by Lutron Electronics Co. of Coopersburg, Pa., in honor of the company's founders and the inventor of the electronic dimmer switch.

-- CMU SCS news, April 5, 2018

#### April 2018 Lorrie Cranor Receives IAPP Leadership Award

Lorrie Cranor has received the 2018 Leadership Award from The International Association of Privacy Professionals (IAPP). Cranor, a professor in the Institute for Software Research and the Department of Engineering and Public Policy, accepted the award at the IAPP's Global Privacy Summit on March 27. "Lorrie Cranor, for 20 years, has been a leading voice and a leader in the privacy field," said IAPP President and CEO Trevor Hughes. "She developed some of the earliest privacy enhancing technologies, she developed a groundbreaking program at Carnegie Mellon University to create future generations of privacy engineers, and she has been a steadfast supporter, participant and leader of the field of privacy for that entire time. Her merits as recipient for our privacy leadership award are unimpeachable. She's as great a person as we have in our world." The IAPP Leadership Award

is given annually to individuals who demonstrate an "ongoing commitment to furthering privacy policy, promoting recognition of privacy issues and advancing the growth and visibility of the privacy profession." Cranor helped develop and is now co-director of CMU's MSIT-Privacy Engineering master's degree program as well as director of the CyLab Usable Privacy and Security Laboratory.

--CMU Piper, April 5, 2018

## April 2018 Welcome Baby Nora!

Pete and Laura Losi, and Grandma Karen Lindenfelser are thrilled to announce Nora Grace joined big sister Layla Anne and big cousin Landon Thomas to become a family of four (five if you count, Rudy, the granddog). Nora was born Friday the 13th at II:50 am at 7 lbs 19.5 inches.

# April 2018 Srinivasan Seshan Appointed Head of CSD

Srinivasan Seshan has been appointed head of the Computer Science Department (CSD), effective July I. He succeeds Frank Pfenning, who will re-

turn to full-time teaching and research. "We are all excited about Srini Seshan's new role as head of CSD," said School of Computer Science

Dean Andrew Moore. "He is an outstanding researcher and teacher, and I'm confident that his expanded role in leadership will help the department reach even greater heights." Seshan joined the CSD faculty in 2000, and served as the department's associate head for graduate education from 2011 to 2015. His research focuses on improving the design, performance and security of computer networks, including wireless and mobile networks. He earned his bachelor's, master's and doctoral degrees in computer science at the University of California, Berkeley. He worked as a research staff member at IBM's T.J. Watson Research Center for five years before joining Carnegie Mellon.

--CMU Piper, April 5, 2018

#### March 2018 Andy Pavlo Wins Google Faculty Research Award

The CMU Database Group and the PDL are pleased to announce that Prof. Andy Pavlo has won a 2018 Google Faculty Research Award. This award was for his research on automatic database management systems. Andy was one of a total 14 faculty members at Carnegie Mellon University selected for this award.

The Google Faculty Research Awards is an annual open call for proposals on computer science and related topics such as machine learning, machine perception, natural language processing, and quantum computing. Grants cover tuition for a graduate student and provide both faculty and students the opportunity to work directly with Google researchers and engineers.

This round received IO33 proposals covering 46 countries and over 360 universities from which I52 were chosen to fund. The subject areas that received the most support this year were human computer interaction, machine learning, machine perception, and systems.

-- Google and CMU Database Group News, March 20, 2018

#### February 2018 Lorrie Cranor Wins Top SIGCHI Award

Lorrie Cranor, a professor in the Institute for Software Research and the Department of Engineering and Public Policy, is this year's recipient of the

Social Impact Award from the Association for Computing Machinery Special Interest Group on Computer Human Interaction (SIGCHI).

The Social Impact Award is given to mid-level or senior individuals who promote the application of humancomputer interaction research to pressing social needs and includes an honorarium of \$5,000, the opportunity to give a talk about the awarded work at the CHI conference, and lifetime invitations to the annual SIGCHI award banquet.

"Lorrie's work has had a huge impact on the ability of non-technical users to protect their security and privacy through her user-centered approach to security and privacy research and development of numerous tools and technologies," said Blase Ur, who prepared Lorrie's nomination. Ur is a former Ph.D. student of Lorrie's, and is now an assistant professor at the University of Chicago.

In addition to Ur, three former students from Cranor's CyLab Usable Privacy and Security Lab – Michelle Mazurek, Florian Schaub and Yang Wang – supported Lorrie's nomination. "All four of us are currently assistant professors, spread out across the United States," said Ur, who received his doctorate degree in 2016. "In addition to this impact on end users, the four of us who jointly nominated her have also benefitted greatly from her mentorship."

A full summary of this year's SIGCHI award recipients can be found on the organization's website.

-- info from Cylab News, Daniel Tkacik, Feb. 23, 2018

## February 2018 Andy Pavlo Awarded a Sloan Fellowship

"The Sloan Research Fellows represent the very best science has to offer," said Sloan President Adam Falk. "The brightest minds, tackling the hardest problems, and succeeding brilliantly — fellows are quite literally the future of 21st century science."

Andrew Pavlo, an assistant professor of computer science, specializes in the study of database management systems, specifically main memory systems, non-relational systems (NoSQL), transaction processing systems (NewS-QL) and large-scale data analytics. He is a member of the Database Group and the Parallel Data Laboratory. He joined the Computer Science Department in 2013 after earning a Ph.D. in computer science at Brown University. He won the 2014 Jim Gray Doctoral Dissertation Award from the Association for Computing Machinery's (ACM) Special Interest Group on the Management of Data.

-- Carnegie Mellon University News, Feb. 15, 2018

#### December 2017 Welcome Baby Sebastian!

In not-unexpected news, David, Erica and big sister Aria are delighted to announce the arrival of a squirmy and

very snuggly addition to their family. Sebastian Alexander Andersen-Fuchs was born December II, 2017, at II:47 am at 8lb 8oz and 21" long. Mom and baby are healthy, and Aria is very excited to be a big sister.

## December 2017 Mor Harchol-Balter and Onur Mutlu Fellows of the ACM

Congratulations to Mor (Professor of CS) and Onur (adjunct Professor of ECE), who have been made Fellows of the ACM.

From the ACM

website: "To be selected as a Fellow is to join our most renowned member grade and an elite group that represents less than I percent of ACM's overall membership," explains ACM President Vicki L. Hanson. "The Fellows program allows us to shine a light on landmark contributions to computing, as well as the men and women whose hard work, dedication, and inspiration are responsible for groundbreaking work that improves our lives in so many ways."

Mor was selected "for contributions to performance modeling and analysis of distributed computing systems."

Onur, who is now at ETH Zurich, was chosen for "contributions to computer architecture research, especially in memory systems."

--with info from www.acm.org

# AWARDS & OTHER PDL NEWS

#### continued from page 9

# November 2017 Welcome Baby Will!

Kevin Hsieh and his wife would like share the news of their new baby! Will was born on November 15, 2017 at 11:15am (not a typo...). He was born at 6lb 7oz and 20" long. Since then, he has been growing very well and keeping his family busy.

October 2017 Welcome Baby Jonas!

Jason & Chien-Chiao Boles are excited to announce the arrival of their son Jonas at 7:42pm, October 18th. Jonas was born a few weeks early — a surprise for us all. Everyone is doing well so far.

# October 2017 Lorrie Cranor Awarded FORE Systems Chair of Computer Science

We are very pleased to announce that, in addition to a long list of accomplishments, which has included a term as the Chief Technologist of the Federal Trade Commission, Lorrie Cranor has been made the FORE Systems Professor of Computer Science and Engineering & Public Policy at CMU. Lorrie provided information that "the founders of FORE Systems, Inc. established the FORE Systems Professorship in 1995 to support a faculty member in the School of Computer Science. The company's name is an acronym formed by the initials of the founders' first names. Before it was acquired by Great Britain's Marconi in 1998, FORE created technology that allows computer networks to link and transfer information at a rapid speed. Ericsson purchased much of Marconi in 2006." The chair was previously held by CMU University Professor Emeritus, Edmund M. Clarke.

# September 2017 Garth Gibson to Lead New Vector Institute for Al in Toronto

In January of 2018, PDL's founder, Garth Gibson, became President and CEO of the Vector Institute for AI in Toronto. Vector's website states

that "Vector will be a leader in the transformative field of artificial intelligence, excelling in machine and deep learning — an area of scientific, academic, and commercial endeavour that will shape our world over the next generation."

Frank Pfenning, Head of the Department of Computer Science, notes that "this is a tremendous opportunity for Garth, but we will sorely miss him in the multiple roles he plays in the department and school: Professor (and all that this entails), Co-Director of the MCDS program, and Associate Dean for Masters Programs in SCS."

We are sad to see him go and will miss him greatly, but the opportunities presented here for world level innovation are tremendous and we wish him all the best.

## June 2017 Satya Honored for Creation of Andrew File System

The Association for Computing Machinery has named the developers of CMU's pioneering Andrew File System (AFS) the recipients of its prestigious 2016 Software System Award.

AFS was the first distributed file system designed for tens of thousands of machines, and pioneered the use of scalable, secure and ubiquitous ac-

cess to shared file data. To achieve the goal of providing a common shared file system used by large networks of people, AFS introduced novel approaches to caching, security, management and administration.

The award recipients, including CS Professor Mahadev Satyanarayanan, built the Andrew File System in the 1980s while working as a team at the Information Technology Center (ITC) — a partnership between Carnegie Mellon and IBM.

The ACM Software System Award is presented to an institution or individuals recognized for developing a software system that has had a lasting influence, reflected in contributions to concepts, in commercial acceptance, or both.

AFS is still in use today as both an open-source system and as a file system in commercial applications. It has also inspired several cloud-based storage applications. Many universities integrated AFS before it was introduced as a commercial application.

-- Byron Spice, The Piper, June 1, 2017

mode of VPIC. For each timestep, 40 bytes of data is produced per particle representing the particle's spatial location, velocity, energy, etc. We refer to the entire particle data written at the same timestep as a frame, because frame data is often used by domain scientists to construct false-color movies of the simulation state over time. Large-scale VPIC simulations have been conducted with up to trillions of particles, generating terabytes of data for each frame.

Domain scientists are often interested in a tiny subset of particles with specific characteristics, such as high energy, that is not known until the simulation ends. All data for each such particle is gathered for further analysis, such as visualizing its trajectory through space over time. Unfortunately, particle data within a frame is written out of order, since output order depends on the particles' spatial location. Therefore, in order to locate individual particles' data over time, all output data must be sorted before they can be analyzed.

For scientists working with VPIC, it would be significantly easier programmatically to create a separate file for each particle, and append a 40-byte data record on each timestep. This would reduce analysis queries to sequentially reading the contents of a tiny number of particle files. Attempting to do this in today's parallel file systems, however, would be disastrous for performance. Expecting existing HPC storage stacks and file systems to adapt to scientific needs such as this one, however, is lunacy. Parallel file systems are designed to be long-running, robust services that work across applications. They are typically kernel resident, mainly developed to manage the hardware, and primarily optimized for large sequential data access. DeltaFS aims to provide this file-per-particle representation to applications, while ensuring that storage hardware is utilized to its full performance potential. A comparison of the file-per-process (current state-ofthe-art) and file-per-particle (DeltaFS) representations is shown in Figure 1.

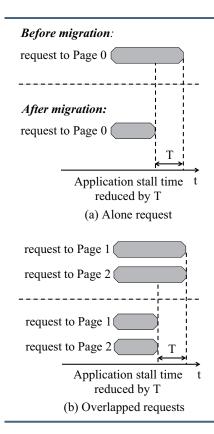

To improve the performance of applications with small I/O access patterns similar to VPIC, we propose an Indexed Massive Directory - a new technique for indexing data in-situ as it is written to storage. In-situ indexing of massive amounts of data written to a single directory simultaneously, and in an arbitrarily large number of files with the goal of efficiently recalling data written to the same file without requiring any timeconsuming data post-processing steps to reorganize it. This greatly improves the readback performance of applications, at the price of small overheads associated with partitioning and indexing the data during writing. We achieve this through a memory-efficient indexing mechanism for reordering and indexing data, and a log-structured storage layout to pack small writes into large log objects, all while ensuring compute node resources are used frugally.

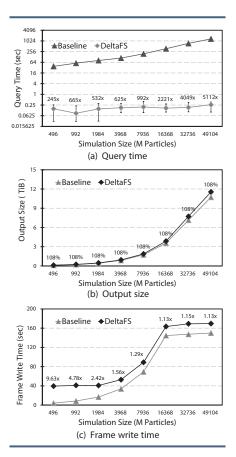

We evaluated the efficiency of the Indexed Massive Directory on LANL's Trinity hardware (Figure 2). By applying in-situ partial sorting of VPIC's particle output, we demonstrated over 5000x speedup in reading a single particle's trajectory from a 48- billion particle simulation output using only a single CPU core, compared to post-processing the entire dataset (IOTiB) using the same amount of CPU cores as the original simulation. This speedup increases with simulation scale, while the total memory used for partial sort is fixed at 3% of the memory available to the simulation code. The cost of this read acceleration is the increased work in the in-situ pipeline and the additional storage capacity dedicated to storing the indexes. These results are encouraging, as they indicate that the output write buffering stage of the software-defined storage stack can be leveraged for one or more forms of efficient in-situ analysis, and can be applied to more kinds of query workloads.

For more information, please see [3] or visit our project page at www.pdl.cmu. edu/DeltaFS/

Figure 2: Results from real VPIC simulation runs with and without DeltaFS at LANL Trinity computer.

#### References

[I] Zheng, Q., Ren, K., Gibson, G., Settlemyer, B. W., and Grider, G. DeltaFS: Exascale file systems scale better without dedicated servers. In Proceedings of the 10th Parallel Data Storage Workshop (PDSW 15), pp. 1–6.

[2] Byna, S., Sisneros, R., Chadalavada, K., and Koziol, Q. Tuning parallel I/O on blue waters for writing 10 trillion particles. In Cray User Group (CUG) (2015).

[3] Qing Zheng, George Amvrosiadis, Saurabh Kadekodi, Garth Gibson, Chuck Cranor, Brad Settlemyer, Gary Grider, Fan Guo. Software-Defined Storage for Fast Trajectory Queries using a DeltaFS Indexed Massive Directory. PDSW-DISCS 2017, Denver, CO, November 2017.

# **3SIGMA**

#### Jun Woo Park, Greg Ganger and PDL 3Sigma Group

## 3Sigma: Distribution-Based Cluster Scheduling for Runtime Uncertainty

Modern cluster schedulers face a daunting task. Modern clusters support a diverse mix of activities, including exploratory analytics, software development and test, scheduled content generation, and customer-facing services [2]. Pending work is typically mapped to heterogeneous resources to satisfy deadlines for business-critical jobs, minimize delays for interactive best-effort jobs, maximize efficiency, and so on. Cluster schedulers are expected to make that happen.

Knowledge of the runtimes of these pending jobs has been identified as a powerful building block for modern cluster schedulers. With it, a scheduler can pack jobs more aggressively in a cluster's resource assignment plan, for instance by allowing a latency-sensitive best-effort job to run before a highpriority batch job provided that the priority job will still meet its deadline. Runtime knowledge allows a scheduler to determine whether it is better to start a job immediately on suboptimal machine types with worse expected performance, wait for the jobs currently occupying the preferred machines to finish, or to preempt them. Exploiting job runtime knowledge leads to better, more robust scheduler decisions than relying on hard-coded assumptions.

In most cases, the job runtime estimates are based on previous runtimes observed for similar jobs (e.g., from the same user or by the same periodic job script). When such estimates are accurate, the schedulers relying on them outperform those using other approaches.

However, we find that estimate errors, while expected in large, multiuse clusters, cover an unexpectedly larger range. Applying a state-of-the-

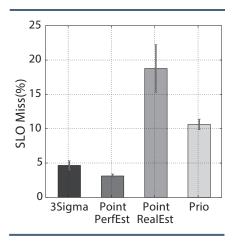

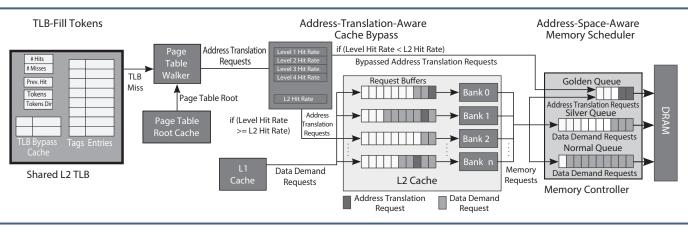

Figure 1: Comparison of 3Sigma with three other scheduling approaches w.r.t. SLO (deadline) miss rate, for a mix of SLO and best effort jobs derived from the Google cluster trace [2] on a 256-node cluster. 3Sigma, despite estimating runtime distributions online with imperfect knowledge of job classification, approaches the performance of a hypothetical scheduler using perfect runtime estimates (PointPerfEst). Full historical runtime distributions and mis-estimation handling helps 3Sigma outperform PointRealEst, a stateof-the-art point-estimate-based scheduler. The value of exploiting runtime information, when done well, is confirmed by comparison to a conventional priority-based approach (Prio).

art ML-based predictor [I] to three real-world traces, including the wellstudied Google cluster trace [2] and new traces from data analysis clusters used at a hedge fund and a scientific site, shows good estimates in general (e.g., 77-92% within a factor of two of the actual runtime and most much closer). Unfortunately, 8-23% are not within that range, and some are off by an order of magnitude or more. Thus, a significant percentage of runtime estimates will be well outside the error ranges previously reported. Worse, we find that schedulers relying on runtime estimates cope poorly with such error profiles. Comparing the middle two bars of Fig. I shows one example of how much worse a state-of-the-art scheduler does with real estimate error

profiles as compared to having perfect estimates.

Our 3Sigma cluster scheduling system uses all of the relevant runtime history for each job rather than just a point estimate derived from it. Instead, it uses expected runtime distributions (e.g., the histogram of observed runtimes), taking advantage of the much richer information (e.g., variance, possible multi-modal behaviors, etc.) to make more robust decisions. The first bar of Fig. I illustrates 3Sigma's efficacy.

By considering the range of possible runtimes for a job, and their likelihoods, 3Sigma can explicitly consider the various potential outcomes from each possible plan and select a plan based on optimizing the expected outcome. For example, the predicted distribution for one job might have low variance, indicating that the scheduler can be aggressive in packing it in, whereas another job's high variance might suggest that it should be scheduled early (relative to its deadline). 3Sigma similarly exploits the runtime distribution to adaptively address the problem of point over-estimates, which may suggest that the scheduler will avoid scheduling a job based on the likelihood of missing its deadline.

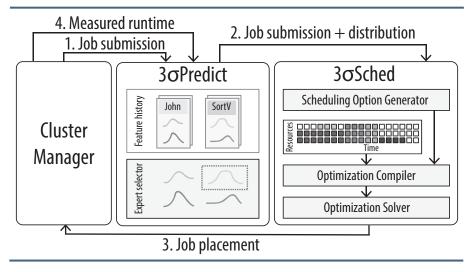

In application, 3Sigma replaces the scheduling component of a cluster manager (e.g. YARN). The cluster manager remains responsible for job and resource life-cycle management.

Job requests are received asynchronously by 3Sigma from the cluster manager (Step I of Fig. 2). As is typical for such systems, the specification of the request includes a number of attributes, such as (I) the name of the job to be run, (2) the type of job to be run (e.g. MapReduce), (3) the user submitting the job, and (4) a specification of the resources requested.

Figure 2: End-to-end system integration

The role of the predictor component 30Predict is to provide the core scheduler with a probability distribution of the execution time of the submitted job. 30Predict does this by maintaining a history of previously executed jobs, identifying a set of jobs that, based on their attributes, are similar to the current job and deriving the runtime distribution the selected jobs' historical runtimes (Step 2 of Fig. 2). Given a distribution of expected job runtimes and request specifications, the core scheduler, 30Sched decides which jobs to place on which resources and when. The scheduler evaluates the expected utility of each option and the expected resource consumption and availability over the scheduling horizon. Valuations and computed resource capacity are then compiled into an optimization problem, which is solved by an external solver. 30Sched translates the solution into an updated schedule and submits the schedule to the cluster manager (Step 3 of Fig. 2). On completion, the job's actual runtime is recorded by 30Predict (along with the attribute information from the job) and incorporated into the job history for future predictions (Step 4 of Fig. 2).

Full system and simulation experi-

ments with production-derived workloads demonstrate 3Sigma's effectiveness. Using its imperfect but automatically-generated history-based runtime distributions, 3Sigma outperforms both a state-of-the-art point-estimatebased scheduler and a priority-based (runtime-unaware) scheduler, especially for mixes of deadline-oriented jobs and latency-sensitive jobs on heterogeneous resources. 3Sigma simultaneously provides higher (I) SLO attainment for deadline-oriented jobs and (2) cluster goodput (utilization).

Our evaluation of 3Sigma, yielded five key takeaways. First, 3Sigma achieves significant improvement over the stateof-the-art in SLO miss rate, best-effort job goodput, and best-effort latency in a fully-integrated real cluster deployment, approaching the performance of the unrealistic PointPerfEst in SLO miss rate and BE latency. Second, all of the 30Sched component features are important, as seen via a piecewise benefit attribution. Third, estimated distributions are beneficial in scheduling even if they are somewhat inaccurate, and such inaccuracies are better handled by distribution-based scheduling than point-estimate-based scheduling. In fact, experiments with trace-derived workloads both on a real 256-node cluster and in simulation demonstrate that 3Sigma's distribution-based scheduling greatly outperforms a state-of-the-art pointestimate scheduler, approaching the performance of a hypothetical scheduler operating with perfect runtime estimates. Fourth, 3Sigma performs well (i.e., comparably to PointPerfEst) under a variety of conditions, such as varying cluster load, relative SLO job deadlines, and prediction inaccuracy. Fifth, we show that the 3Sigma components ( $3\sigma$ Predict and  $3\sigma$ Sched) can scale to >10000 nodes. Overall, we see that 3Sigma robustly exploits runtime distributions to improve SLO attainment and best-effort performance, dealing gracefully with the complex runtime variations seen in real cluster environments.

For more information, please see [3] or visit www.pdl.cmu.edu/TetriSched/

#### References

[I] Alexey Tumanov, Angela Jiang, Jun Woo Park, Michael A. Kozuch, and Gregory R. Ganger. 2016. JamaisVu: Robust Scheduling with AutoEstimated Job Runtimes. Technical Report CMU-PDL-16-104. Carnegie Mellon University.

[2] Charles Reiss, Alexey Tumanov, Gregory R. Ganger, Randy H. Katz, and Michael A. Kozuch. 2012. Heterogeneity and Dynamicity of Clouds at Scale: Google Trace Analysis. In Proc. of the 3nd ACM Symposium on Cloud Computing (SOCC '12).

[3] Jun Woo Park, Alexey Tumanov, Angela Jiang, Michael A. Kozuch, Gregory R. Ganger. 3Sigma: Distribution-based Cluster Scheduling for Runtime Uncertainty. EuroSys '18, April 23–26, 2018, Porto, Portugal.

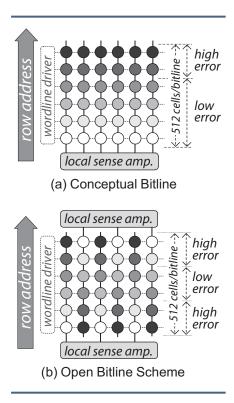

#### DISSERTATION ABSTRACT: Architectural Techniques for Improving NAND Flash Memory Reliability

Yixin Luo Carnegie Mellon University, SCS PhD Defense — February 9, 2018

Raw bit errors are common in NAND flash memory and will increase in the future. These errors reduce flash reliability and limit the lifetime of a flash memory device. This dissertation improves flash reliability with a multitude of low-cost architectural techniques. We show that NAND flash memory reliability can be improved at low cost and with low performance overhead by deploying various architectural techniques that are aware of higher-level application behavior and underlying flash device characteristics.

This dissertation analyzes flash error characteristics and workload behavior through rigorous experimental characterization and designs new flash controller algorithms that use the insights gained from our analysis to improve flash reliability at low cost. We investigate four novel directions. (I) We propose a new technique called WARM that improves flash lifetime by 12.9 times by managing flash retention differently for write-hot data and write-cold data. (2) We propose a new framework that learns an online flash channel model for each chip and enables four new flash controller algorithms to improve flash write endurance by up to 69.9%. (3) We identify three new error characteristics in 3D

Industry guests and CMU folks boarding the bus to head to Bedford Springs for the PDL Retreat

NAND flash memory through comprehensive experimental characterization of real 3D NAND chips, and propose four new techniques that mitigate these new errors and improve 3D NAND raw bit error rate by up to 66.9%. (4) We propose a new technique called HeatWatch that improves 3D NAND lifetime by 3.85 times by utilizing the self-healing effect to mitigate retention errors in 3D NAND.

DISSERTATION ABSTRACT: Fast Storage for File System Metadata Kai Ren

Carnegie Mellon University, SCS PhD Defense — August 8, 2017

In an era of big data, the rapid growth of data that many companies and organizations produce and manage continues to drive efforts to improve the scalability of storage systems. The number of objects presented in storage systems continue to grow, making metadata management critical to the overall performance of file systems. Many modern parallel applications are shifting toward shorter durations and larger degree of parallelism. Such trends continue to make storage systems to experience more diverse metadata intensive workloads.

The goal of this dissertation is to improve metadata management in both local and distributed file systems. The dissertation focuses on two aspects. One is to improve the out-of-core representation of file system metadata, by exploring the use of log-structured multi-level approaches to provide a unified and efficient representation for different types of secondary storage devices (e.g., traditional hard disk and solid state disk). We have designed and implemented TableFS and its improved version SlimFS, which shows 50% to 10x faster than traditional Linux file systems. The other aspect is to demonstrate that such representation also can be flexibly integrated with many namespace distribution mechanisms to scale metadata performance of distribution file systems, and

Greg Ganger, PDL alum Michael Abd-El-Malek (Google), and Bill Courtright enjoy social time at the PDL Retreat.

provide better support for a variety of big data applications in data center environment. Our distributed metadata middleware IndexFS can help improve metadata performance for PVFS, Lustre and HDFS by scaling to as many as 128 metadata servers.

# DISSERTATION ABSTRACT: Enabling Data-Driven Optimization of Quality of Experience in Internet Applications

Junchen Jiang Carnegie Mellon University, SCS PhD Defense — June 23, 2017

Today's Internet has become an eyeball economy dominated by applications such as video streaming and VoIP. With most applications relying on user engagement to generate revenues, maintaining high user-perceived Quality of Experience (QoE) has become crucial to ensure high user engagement.

For instance, one short buffering interruption leads to 39% less time spent watching videos and causes significant revenue losses for ad-based video sites. Despite increasing expectations for high QoE, existing approaches have limitations to achieve the QoE needed by today's applications. They either require costly re-architecting of the network core, or use suboptimal endpoint-based protocols to react to the dynamic Internet performance based on limited knowledge of the network.

Shinya Matsusmoto (Hltachi) talks about his company's research on "Risk-aware Data Replication against Widespread Disasters" at the PDL retreat industry poster session.

In this thesis, I present a new approach, which is inspired by the recent success of data-driven approaches in many fields of computing. I will demonstrate that datadriven techniques can improve Internet QoE by utilizing a centralized real-time view of performance across millions of endpoints (clients). I will focus on two fundamental challenges unique to this data-driven approach: the need for expressive models to capture complex factors affecting QoE, and the need for scalable platforms to make real-time decisions with fresh data from geo-distributed clients.

Our solutions address these challenges in practice by integrating several domain-specific insights in networked applications with machine learning algorithms and systems, and achieve better QoE than using many standard machine learning solutions. I will present end-to-end systems that yield substantial QoE improvement and higher user engagement for video streaming and VoIP. Two of my projects, CFA and VIA, have been used in industry by Conviva and Skype, companies that specialize in QoE optimization for video streaming and VoIP, respectively.

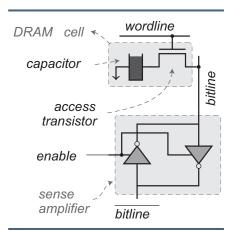

# DISSERTATION ABSTRACT: Understanding and Improving the Latency of DRAM-Based Memory System

Kevin K. Chang Carnegie Mellon University, ECE PhD Defense — May 5, 2017

Over the past two decades, the storage capacity and access bandwidth of main memory have improved tremendously, by 128x and 20x, respectively. These improvements are mainly due to the continuous technology scaling of DRAM (dynamic random-access memory), which has been used as the physical substrate for main memory. In stark contrast with capacity and bandwidth, DRAM latency has remained almost constant, reducing by only 1.3x in the same time frame. Therefore, long DRAM latency continues to be a critical performance bottleneck in modern systems. Increasing core counts, and the emergence of increasingly more data-intensive and latencycritical applications further stress the importance of providing low-latency memory accesses.

In this dissertation, we identify three main problems that contribute significantly to long latency of DRAM accesses. To address these problems, we present a series of new techniques. Our new techniques significantly improve both system performance and energy efficiency. We also examine the critical relationship between supply voltage and latency in modern DRAM chips and develop new mechanisms that exploit this voltage-latency tradeoff to improve energy efficiency.

First, while bulk data movement is a key operation in many applications

Saurabh Kadekodi discusses his research on "Aging Gracefully with Geriatrix: A File System Aging Suite" at a PDL retreat poster session.

and operating systems, contemporary systems perform this movement inefficiently, by transferring data from DRAM to the processor, and then back to DRAM, across a narrow offchip channel. The use of this narrow channel for bulk data movement results in high latency and high energy consumption. This dissertation introduces a new DRAM design, Low-cost Inter-linked SubArrays (LISA), which provides fast and energy-efficient bulk data movement across sub- arrays in a DRAM chip. We show that the LISA substrate is very powerful and versatile by demonstrating that it efficiently enables several new architectural mechanisms, including low-latency data copying, reduced DRAM access latency for frequently-accessed data, and reduced preparation latency for subsequent accesses to a DRAM bank.

Second, DRAM needs to be periodically refreshed to prevent data loss due to leakage. Unfortunately, while DRAM is being refreshed, a part of it becomes unavailable to serve memory requests, which degrades system performance. To address this refresh interference problem, we propose two access-refresh parallelization techniques that enable more overlapping of accesses with refreshes inside DRAM, at the cost of very modest changes to the memory controllers and DRAM chips. These two techniques together achieve performance close to an idealized system that does not require refresh.

Third, we find, for the first time, that there is significant latency variation in accessing different cells of a single DRAM chip due to the irregularity in the DRAM manufacturing process. As a result, some DRAM cells are inherently faster to access, while others are inherently slower. Unfortunately, existing systems do not exploit this variation and use a fixed latency value based on the slowest cell across all DRAM chips. To exploit latency variation within the DRAM chip, we

# **DEFENSES & PROPOSALS**

#### continued from page 15

Jiri Schindler (HPE), Bruce Wilson (Broadcom) and Rajat Kateja discuss PDL research at a retreat poster session.

experimentally characterize and understand the behavior of the variation that exists in real commodity DRAM chips. Based on our characterization, we propose Flexible-LatencY DRAM (FLY-DRAM), a mechanism to reduce DRAM latency by categorizing the DRAM cells into fast and slow regions, and accessing the fast regions with a reduced latency, thereby improving system performance significantly. Our extensive experimental characterization and analysis of latency variation in DRAM chips can also enable development of other new techniques to improve performance or reliability.

Fourth, this dissertation, for the first time, develops an understanding of the latency behavior due to another important factor-supply voltage, which significantly impacts DRAM performance, energy consumption, and reliability. We take an experimental approach to understanding and exploiting the behavior of modern DRAM chips under different supply voltage values. Our detailed characterization of real commodity DRAM chips demonstrates that memory access latency reduces with increasing supply voltage. Based on our characterization, we propose Voltron, a new mechanism that improves system energy efficiency by dynamically adjusting the DRAM supply voltage based on a performance model. Our extensive experimental data on the relationship between DRAM supply voltage, latency, and reliability can further enable developments of other new mechanisms that improve latency, energy efficiency, or reliability.

The key conclusion of this dissertation is that augmenting DRAM architecture with simple and low-cost features, and developing a better understanding of manufactured DRAM chips together leads to significant memory latency reduction as well as energy efficiency improvement. We hope and believe that the proposed architectural techniques and detailed experimental data on real commodity DRAM chips presented in this dissertation will enable developments of other new mechanisms to improve the performance, energy efficiency, or reliability of future memory systems.

#### THESIS PROPOSAL: Towards Space-Efficient High-Performance In-Memory Search Structures

Huanchen Zhang, SCS April 30, 2018

This thesis seeks to address the challenge of building space-efficient yet high-performance in-memory search structures, including indexes and filters, to allow more efficient use of memory in OLTP databases. We show that we can achieve this goal by first designing fast static structures that leverage succinct data structures to approach the information-theoretic optimum in space, and then using the "hybrid index" architecture to obtain dynamicity with bounded and modest cost in space and performance.

To obtain space-efficient yet highperformance static data structures, we first introduce the Dynamic-to-Static rules that present a systematic way to convert existing dynamic structures to smaller immutable versions. We then present the Fast Succinct Trie (FST) and its application, the Succinct Range Filter (SuRF), to show how to leverage theories on succinct data structures to build static search structures that consume space close to the informationtheoretic minimum while performing comparably to uncompressed indexes. To support dynamic operations such as inserts, deletes, and updates, we introduce the dual-stage hybrid index architecture that preserves the space efficiency brought by a compressed static index, while amortizing its performance overhead on dynamic operations by applying modifications in batches.

In the proposed work, we seek opportunities to further shrink the size of in-memory indexes by co-designing the indexes with the in-memory tuple storage. We also propose to complete the hybrid index work by extending the techniques to support concurrent indexes.

#### THESIS PROPOSAL: Efficient Networked Systems for Datacenter Fabrics with RPCs

Anuj Kalia, SCS March 23, 2018

Datacenter networks have changed radically in recent years. Their bandwidth and latency has improved by orders of magnitude, and advanced network devices such as NICs with Remote Direct Memory Access (RDMA) capabilities and programmable switches have been deployed. The conventional wisdom is that to best use fast datacenter networks, distributed systems must be redesigned to offload processing from server CPUs to network devices. In this dissertation, we show that conventional, non-offloaded designs offer

Bill Bolosky (Microsoft Research) talks about his company's work on exciting new projects at the PDL retreat industry poster session.

better or comparable performance for a wide range of datacenter workloads, including key-value stores, distributed transactions, and highly-available replicated services.

We present the following principle: The physical limitations of networks must inform the design of high-performance distributed systems.

Offloaded designs often require more network round trips than conventional CPU-based designs, and therefore have fundamentally higher latency. Since they require more network packets, they also have lower throughput. Realizing the benefits of this principle requires fast networking software for CPUs. To this end, we undertake a detailed exploration of datacenter network capabilities, CPU-NIC interaction over the system bus, and NIC hardware architecture. We use insights from this study to create highperformance remote procedure call implementations for use in distributed systems with active end host CPUs.

We demonstrate the effectiveness of this principle through the design and evaluation of four distributed inmemory systems: a key-value cache, a networked sequencer, an online transaction processing system, and a state machine replication system. We show that our designs often simultaneously outperform the competition in performance, scalability, and simplicity.

# THESIS PROPOSAL: Design & Implementation of a Non-Volatile Memory Database Management System

#### Joy Arulraj, SCS December 7, 2017

For the first time in 25 years, a new non-volatile memory (NVM) category is being created that is two orders of magnitude faster than current durable storage media. This will fundamentally change the dichotomy between volatile memory and durable storage in DB systems. The new NVM devices are almost as fast as DRAM, but all writes

Joan Digney and Garth Gibson celebrate 25 years of PDL research and retreats.

to it are potentially persistent even after power loss. Existing DB systems are unable to take full advantage of this technology because their internal architectures are predicated on the assumption that memory is volatile. With NVM, many components of legacy database systems are unnecessary and will degrade the performance of data intensive applications.

This dissertation explores the implications of NVM for database systems. It presents the design and implementation of Peloton, a new database system tailored specifically for NVM. We focus on three aspects of a database system: (I) logging and recovery, (2) storage management, and (3) indexing. Our primary contribution in this dissertation is the design of a new logging and recovery protocol, called write-behind logging, that improves the availability of the system by more than two orders of magnitude compared to the ubiquitous write- ahead logging protocol. Besides improving availability, we found that write- behind logging improves the space utilization of the NVM device and extends its lifetime. Second, we propose a new storage engine architecture that leverages the durability and byte-addressability properties of NVM to avoid unnecessary data duplication. Third, the dissertation presents the design of a latchfree range index tailored for NVM that supports near-instantaneous recovery without requiring special-purpose recovery code.

#### THESIS PROPOSAL: STRADS: A New Distributed Framework for Scheduled Model-Parallel Machine Learning

Jin Kyu Kim, SCS May 15, 2017

Machine learning (ML) methods are used to analyze data which are collected from various sources. As the problem size grows, we turn to distributed parallel computation to complete ML training in a reasonable amount of time. However, naive parallelization of ML algorithms often hurts the effectiveness of parameter updates due to the dependency structure among model parameters, and a subset of model parameters often bottlenecks the completion of ML algorithms due to the uneven convergence rate. In this proposal, I propose two efforts: I) STRADS that improves the training speed in an order of magnitude and 2) STRADS-AP that makes parallel ML programming easier.

In STRADS, I will first present scheduled model-parallel approach with two specific scheduling schemes: I) model parameter dependency checking to avoid updating dependent parameters concurrently; 2) parameter prioritization to give more update chances to the parameters far from its convergence point. To efficiently run the scheduled model-parallel in a distributed system,

Yixin Luo and and Michael Kuchnik, ready to discuss their research on "Error Characterization, Mitigation, and Recovery in Flash Memory Based Solid-State Drives" and "Machine Learning Based Feature Tracking in HPC Simulations" at a PDL retreat poster session.

# **DEFENSES & PROPOSALS**

#### continued from page 17

I implement a prototype framework called STRADS. STRADS improves the parameter update throughput by pipelining iterations and overlapping update computations with network communication for parameter synchronization. With ML scheduling and system optimizations, STRADS improves the ML training time by an order of magnitude. However, these performance gains are at the cost of extra programming burden when writing ML schedules. In STRADS-AP, I will present a high-level programming library and a system infrastructure that automates ML scheduling. The

Dana Van Aken presents her research on "Automatic Database Management System Tuning Through Large-scale Machine Learning" at the PDL retreat.

STRADS-AP library consist of three programming constructs: I) a set of distributed data structures (DDS); 2) a set of functional style operators; and 3) an imperative style loop operator. Once an ML programmer writes an ML program using STRADS-AP library APIs, the STRADS-AP runtime automatically parallelizes the user program over a cluster ensuring data consistency.